23

I

2

C Controller Register Definitions

Slave Address Register

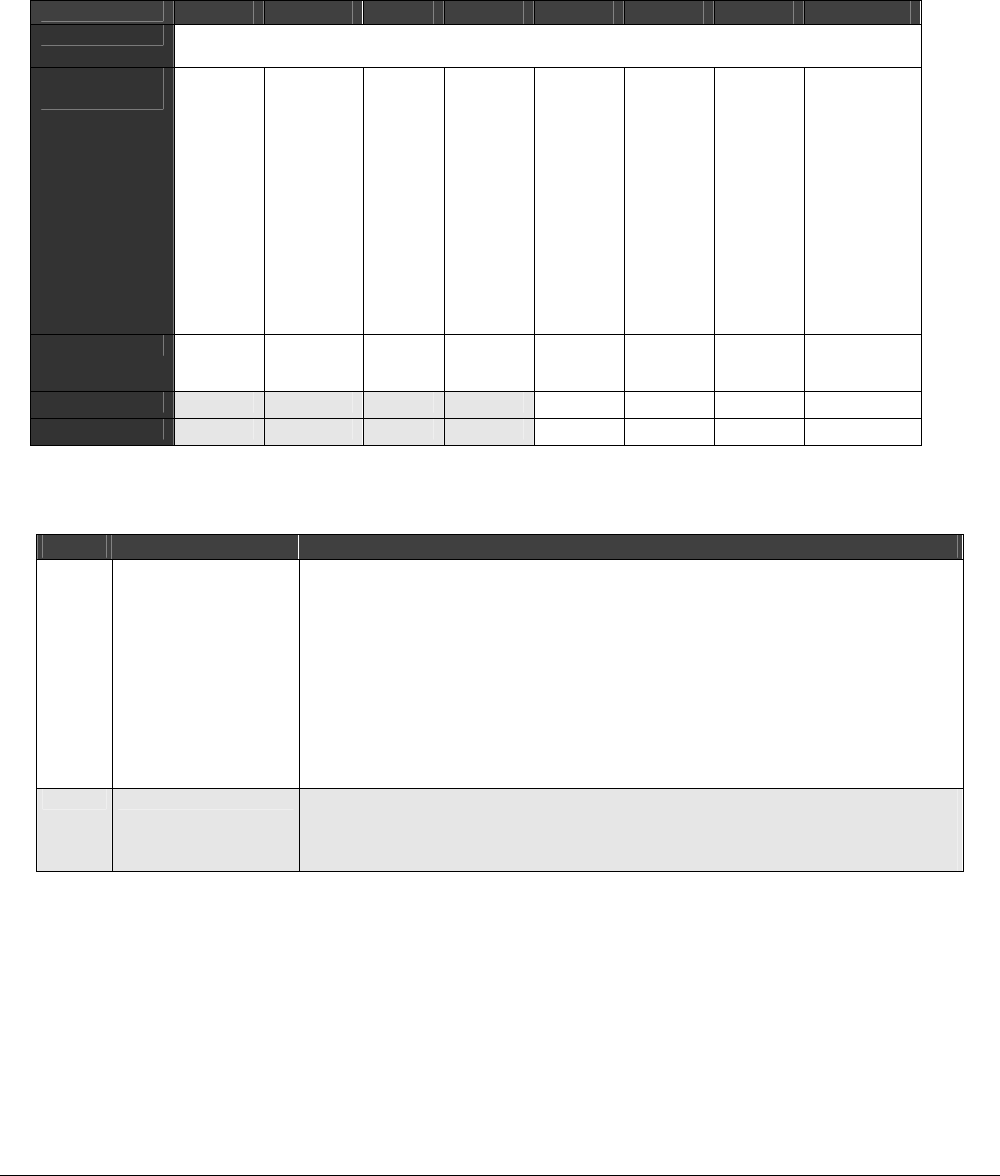

Table 3-8. Slave Address Register

BIT

7 6 5 4 3 2 1 0

OFFSET

D000

EXTENDED

ADDRESS

1 1 1 1 0 SLAX9 SLAX8

General Call Address Enable

FIELD

SLA6 SLA5 SLA4 SLA3 SLA2 SLA1 SLA0 GCE

RESET

0 0 0 0 0 0 0 0

RW

RW RW RW RW RW RW RW RW

Table 3-9. Address Register Definitions

Bits Field Name Description

7:1 SLA6 – SLA0

Slave Address

For 7-bit addressing, these bits are the 7-bit address of the I

2

C controller in slave

mode. When the I

2

C controller receives this address after a START condition, it

generates an interrupt and enters slave mode. (SLA6 corresponds to the first bit

received from the I

2

C bus.)

For 10-bit addressing, when the address received starts with F0h-F7h, the I

2

C

controller recognizes the correspondence to SLAX9 and SLAX8 of an extended

address, and sends an ACK. (The device does not generate an interrupt at this

point.) After receiving the next address byte, the I

2

C controller generates an

interrupt and enters slave mode.

0 GCE

General Call Address Enable

1 = I

2

C controller recognizes the general-call address at 00h (7-bit addressing).

0 = I

2

C controller does not recognize the general-call address at 00h (7-bit

addressing).