83

Frame Reference Register

The Frame Reference register contains information of the current bit of the CAN message. A

frame reference pointer indicates the current bit position. This enables message tracing on bit

level.

Note: The reset value of this register’s bits is indeterminate.

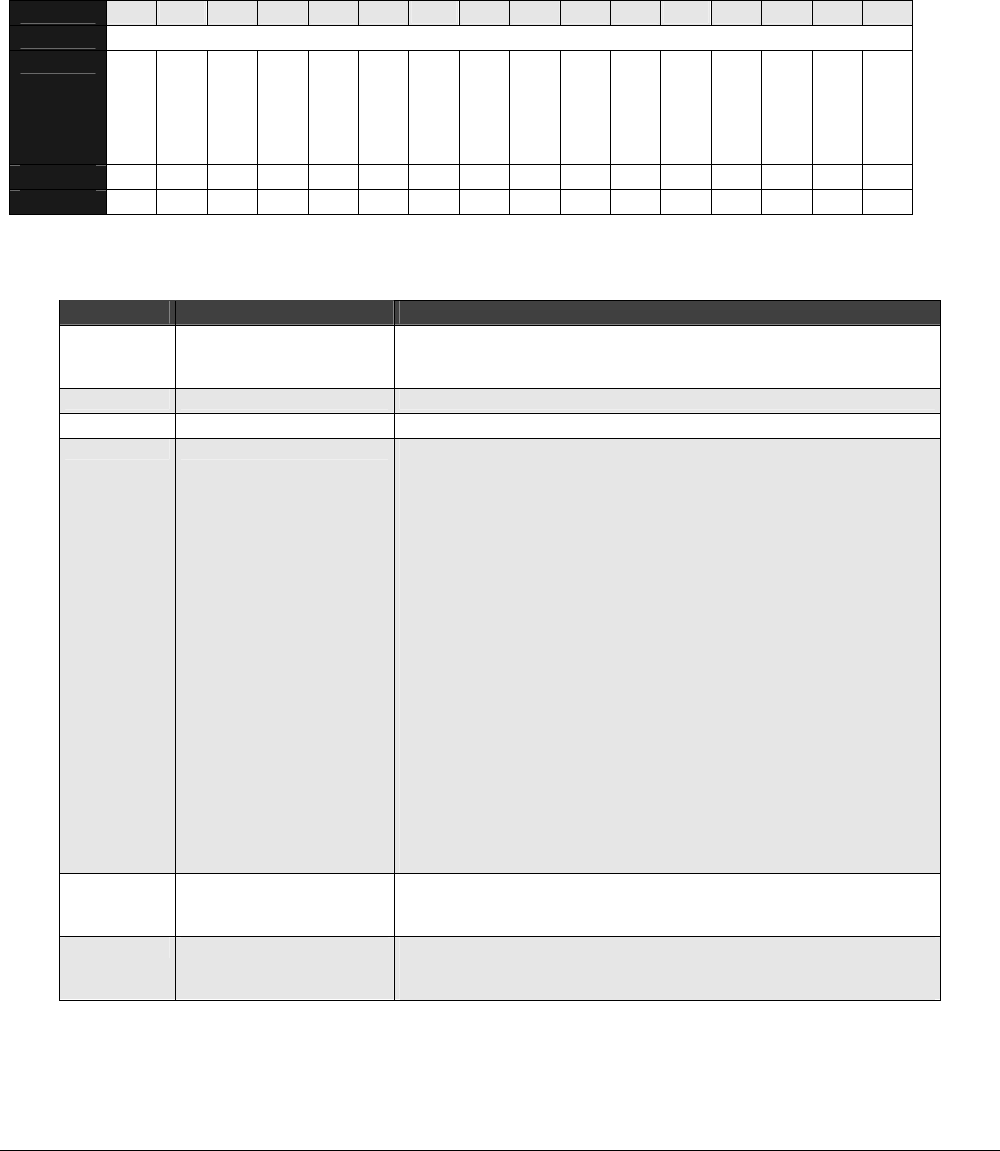

Table 5-64. Frame Reference Register

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 7Ah

FIELD

STUFF_IND

RX_BIT

TX_BIT

FR4

FR3

FR2

FR1

FR0

RX_MOD

TX_MOD

FRB5

FRB4

FRB3

FRB2

FRB1

FRB0

RESET

− − − − − − − − − − − − − − − −

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Table 5-65. Error Capture Register Definitions

Bits Field Name Description

15 STUFFIND

Stuff Bit Inserted

1 = a stuff bit has been inserted.

0 = idle.

14 RX_BIT

Bit State on the Receiver Line

13 TX_BIT

Bit State on the Transmitter Line

12:8 FR[4:0]

frame_ref_Field

This is the frame reference a incoming or outgoing CAN message.

It is coded as follows:

00000 = stopped

00001 = synchronize

00101 = interframe

00110 = bus_idle

00111 = start_of_frame

01000 = arbitration

01001 = control

01010= data

01011 = crc

01100 = ack

01101 = end_of_frame

10000 = error_flag

10001 = error_echo

10010 = error_del:

11000 = overload_flag

11001 = overload_echo

11010 = overload_del

Other codes are not used.

7 RX_MOD

RX Mode

1 = receiving data.

0 = not in RX mode (transmitting or idle).

6 TX_MOD

TX Mode

1 = transmitting data.

0 = not in TX mode (receiving or idle).