41

Error Register

The Error register contains bits for each of the error sources in the USB. Each of these bits is

qualified with its respective error enable bits. The result is OR’ed together and sent to the

ERROR bit of the Interrupt Status register. Once an interrupt bit has been set it may only be

cleared by writing a one to the respective interrupt bit. Each bit is set as soon as the error

condition is detected. Therefore, the interrupt typically will not correspond with the end of a

token being processed. The Error register contains enable bits for each of the error interrupt

sources within the USB. Setting any of these bits enables the respective error interrupt source

in the ERROR register. This register contains the hex value 0000 after a reset (all errors

disabled).

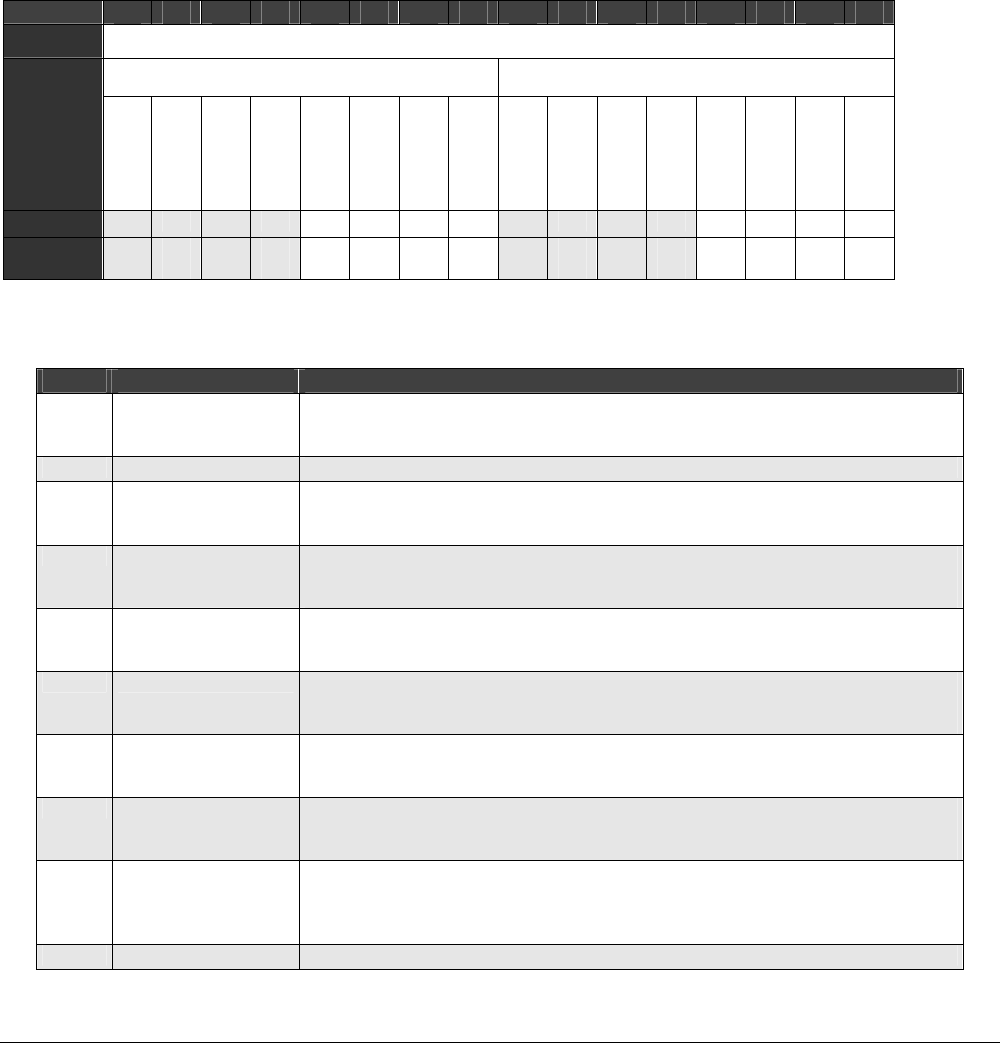

Table 4-10. Error Interrupt Status Register

BIT

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET

02h

Error Mask Error Status

FIELD

BITSERR

///

DMAERR

BTOERR

DFN8

CRC16

CRC5EOF

PIDERR

BITSERR

///

DMAERR

BTOERR

DFN8

CRC16

CRC5EOF

PIDERR

RESET

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

RW

R

W

R

W

R

W

R

W

R

W

R

W

R

W

R

W

R

W

R

W

R

W

R

W

R

W

R

W

R

W

R

W

Table 4-11. 16- Error Interrupt Status Register Definitions

Bits Field Name Description

15 BITSERR

Enable/Disable BITSERR Interrupt

1 = enable the BITSERR interrupt.

0 = disable the BITSERR interrupt (default).

14 ///

Reserved

13 DMAERR

Enable/Disable DMAERR Interrupt

1 = enable the DMAERR interrupt.

0 = disable the DMAERR interrupt (default).

12 BTOERR

Enable/Disable BTOERR Interrupt

1 = enable the BTOERR interrupt.

0 = disable the BTOERR interrupt (default).

11 DFN8

Enable/Disable DFN8 Interrupt

1 = enable the DFN8 interrupt.

0 = disable the DFN8 interrupt (default).

10 CRC16

Enable/Disable CRC16 Interrupt

1 = enable the CRC16 interrupt.

0 = disable the CRC16 interrupt (default).

9 CRC5\EOF

Enable/Disable CRC5/EOF Interrupt

1 = enable the CRC5/EOF interrupt.

0 = disable the CRC5/EOF interrupt (default).

8 PID_ERR

Enable/Disable PID_ERR Interrupt

1 = enable the PID_ERR interrupt.

0 = disable the PID_ERR interrupt (default).

7 BITSERR

Bit Stuff Error

1 = a bit stuff error has been detected. If this bit is set, the corresponding packet

will be rejected due to a bit stuff error.

0 = a bit stuff error has not been detected (default).

6 ///

Reserved