100 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Chapter 10: Configuration and Status

Tri-Mode Ethernet MAC Address Space

When the core is generated in “EDK pcore Format” for import into EDK and connection to

the xps_ll_temac, the address space defined in this section is not included and the address

space will return 0s for a read and all writes will be ignored.

When the core is generated in “Standard CORE Generator Format”, the address space of

the Ethernet MAC is incorporated into the address space of the Ethernet AVB Endpoint

core as illustrated in Figure 10-3. The Ethernet MAC Address space is then split into two

sections:

• “MAC Configuration and Statistics”

• “MAC MDIO Registers”

MAC Configuration and Statistics

Table 10-17 defines the statistic registers and configuration registers of the Tri-Mode

Ethernet MAC core. These are listed with their assigned addresses. See the Tri-Mode

Ethernet MAC User Guide (UG138

) and the Ethernet Statistics User Guide (UG170) for

additional descriptions of these registers.

MAC Address Filter Registers

The Address Filter, optionally present in the Tri-Mode Ethernet MAC LogiCORE™ IP

solution, must not used. Instead, new“Legacy MAC Header Filters” have been added to

the Receiver Legacy Traffic path, which is capable of providing address recognition for

eight unique MAC addresses. See “MAC Header Filter Configuration.”

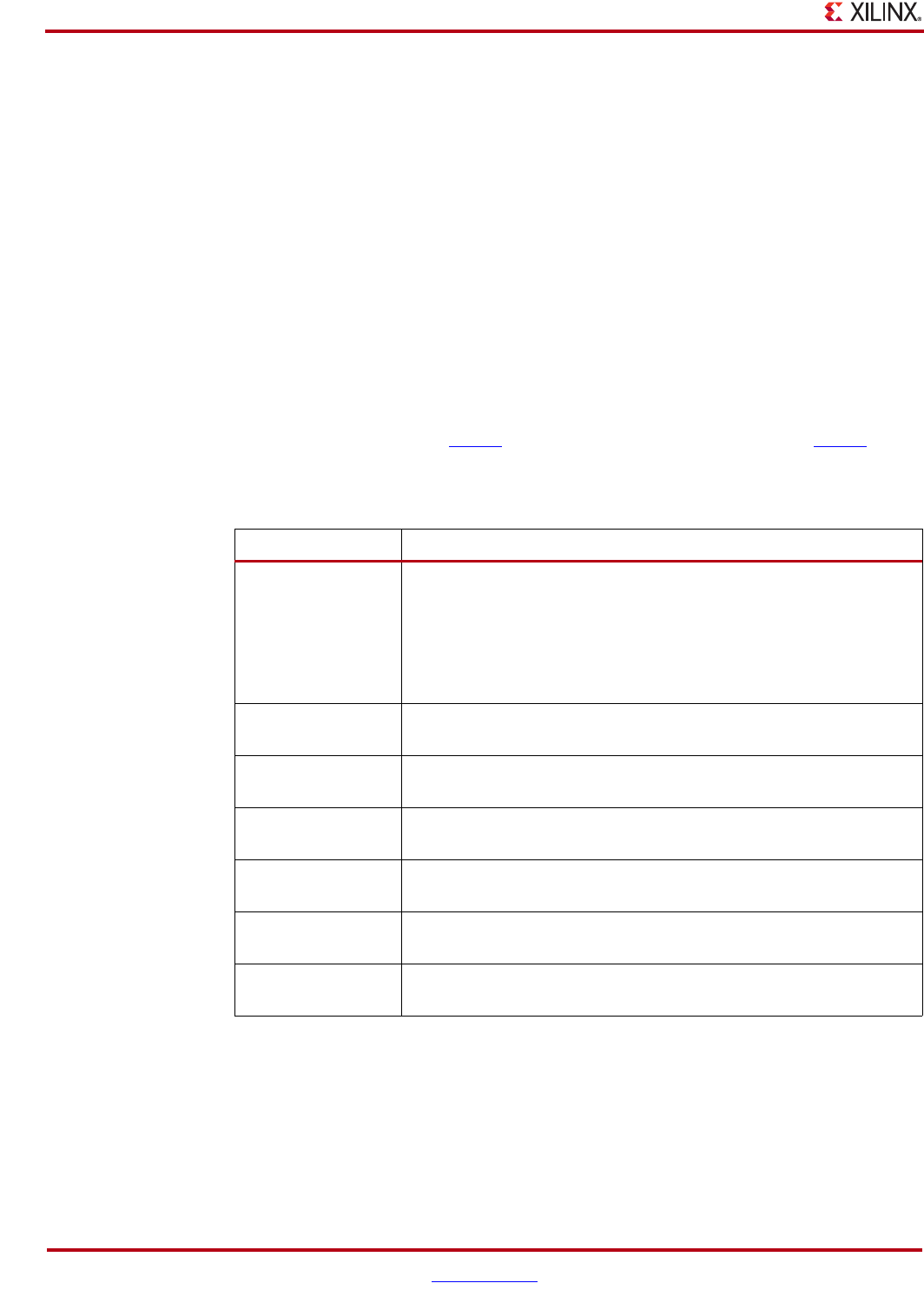

Table 10-17: Tri-Mode Ethernet MAC and Ethernet Statistics

Configuration Registers

Address Description

(PLB_base_address

+ 0x4000)

to

(PLB_base_address

+ 0x41FF)

A maximum of 64 configurable Ethernet MAC statistics registers can

be accessed through the PLB interface (let the statistics registers be

numbered by STATISTIC_NUMBER, from 0 to 63). Each statistic

returns a 64-bit counter value. Accordingly:

Address of STATISTIC_NUMBER =

(PLB_base_address + 0x4000 + [STATISTIC_NUMBER * 8])

PLB_base_address +

0x5000

Receiver Configuration (Word 0)

PLB_base_address +

0x5200

Receiver Configuration (Word 1)

PLB_base_address +

0x5400

Transmitter Configuration

PLB_base_address +

0x5600

Flow Control Configuration

PLB_base_address +

0x5800

MAC Speed Configuration

PLB_base_address +

0x5A00

Management Configuration