86 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Chapter 9: Precise Timing Protocol Packet Buffers

The “Software Drivers” provided with the core, using the PLB and dedicated interrupt,

will use this interface to decode, and then act on, the received PTP packet information.

X-Ref Target - Figure 9-2

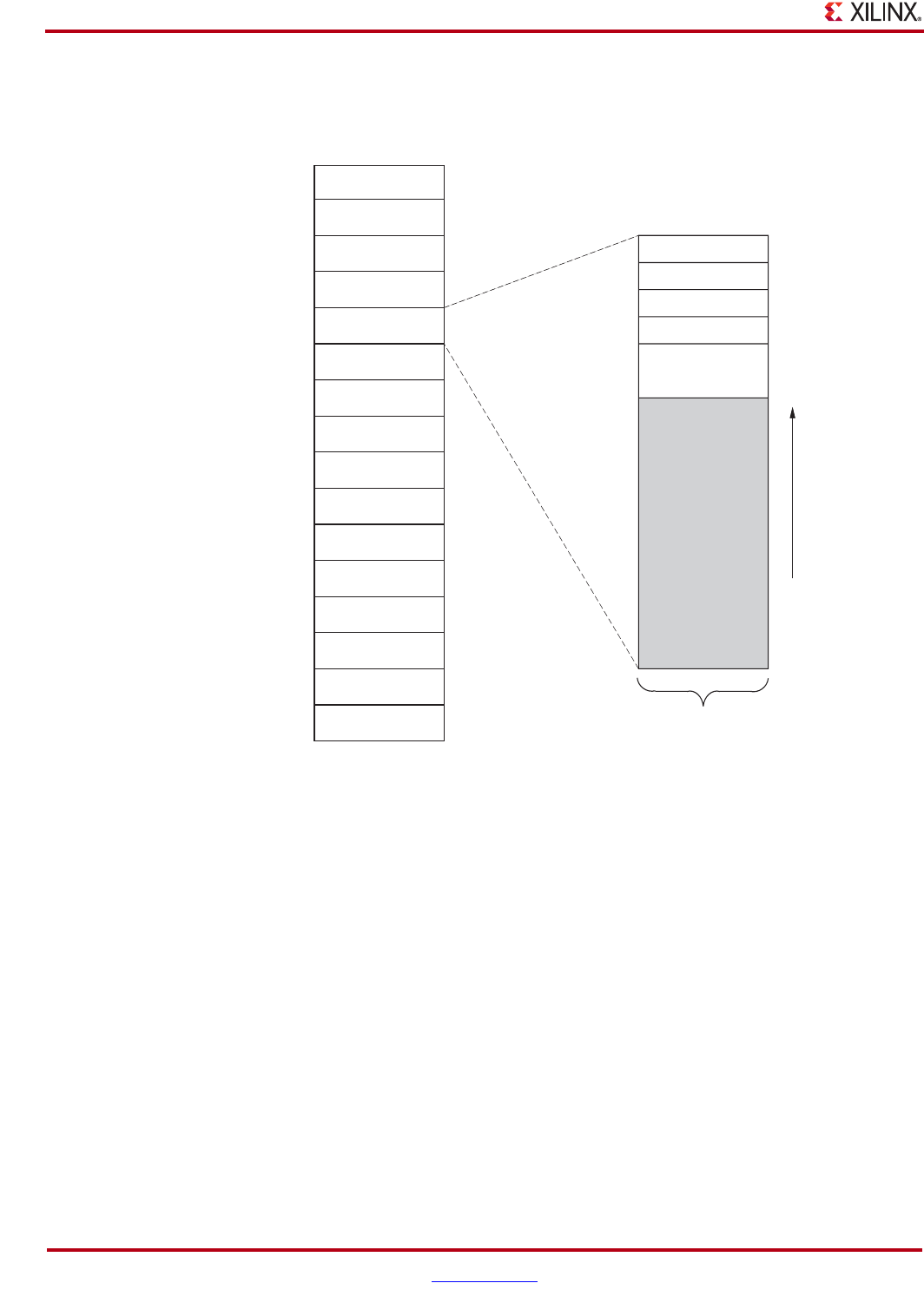

Figure 9-2: Rx PTP Packet Buffer

Rx PTP Packet Buffers

Buffer Number Buffer Base Address

0

1

2

3

4

5

6

7

0x0000

0x0100

0x0200

0x0300

0x0400

0x0500

0x0600

0x0700

Single Rx PTP Packet Buffer

Address (+ Buffer Base Address)

byte-wide data

0xFF

0xFE

0xFD

0xFC

0x00

frame size

PTP Frame Data

unused

timestamp[7:0]

timestamp[15:8]

timestamp[23:16]

timestamp[31:24]

0x0800

0x0900

0x0A00

0x0B00

0x0C00

0x0D00

0x0E00

0x0F00

8

9

10

11

12

13

14

15