Ethernet AVB Endpoint User Guide www.xilinx.com 73

UG492 July 23, 2010

Rx AV Traffic I/F

Rx AV Traffic I/F

The signals forming the Rx AV Traffic I/F are defined in Table 5-5. all signals are

synchronous to the Tri-Mode Ethernet MAC receiver clock, rx_clk, which must always

be qualified by the corresponding clock enable, rx_clk_en (see Table 5-1).

This interface is intentionally identical to the legacy receiver interface (there is a one-to-one

correspondence between signal names when the legacy_ prefix is exchanged for the

av_ prefix).

Error Free AV Traffic Reception

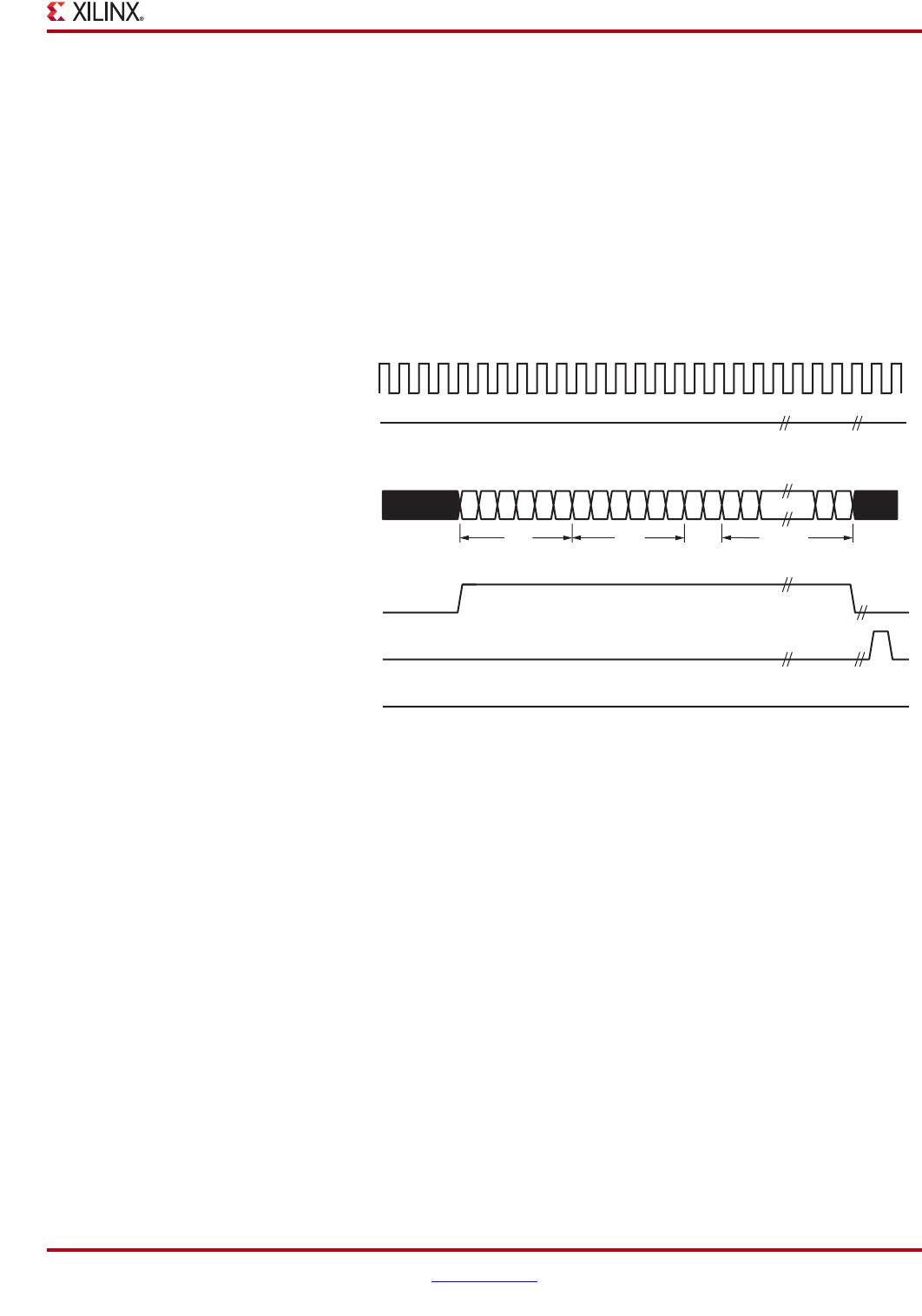

Figure 7-7 illustrates the timing of a normal inbound frame transfer. The AV client must be

prepared to accept data at any time; there is no buffering within the core to allow for

latency in the receive client. After frame reception begins, data is transferred on

consecutive clock enabled cycles to the AV receive client until the frame is complete. The

core asserts the av_rx_frame_good to indicate that the frame was intended for the AV

traffic client, and was successfully received without error.

X-Ref Target - Figure 7-7

Figure 7-7: Normal Frame Reception across the AV Traffic Interface

rx_clk

av_rx_data[7:0]

av_rx_data_valid

av_rx_frame_good

rx_clk_enable

DA SA DAT AL/T

av_rx_frame_bad