Ethernet AVB Endpoint User Guide www.xilinx.com 143

UG492 July 23, 2010

Chapter 15

Detailed Example Design (Standard

Format)

This chapter provides detailed information about the core when generated for the

Standard CORE Generator™ software format. This option is selected from page 1 of the

customization GUI and will deliver the core with the standard CORE Generator software

directory structure (used by many LogiCORE™ IP systems including all other CORE

Generator software Ethernet cores).

This chapter provides detailed information on the core and example design, including a

description of files and the directory structure generated by the Xilinx CORE Generator

software, the purpose and contents of the provided scripts, the contents of the example

HDL wrappers, and the operation of the demonstration test bench.

Please refer to Chapter 16, “Detailed Example Design (EDK format).” when targeting the

Embedded Development Kit.

top directory link - white tex t invisible

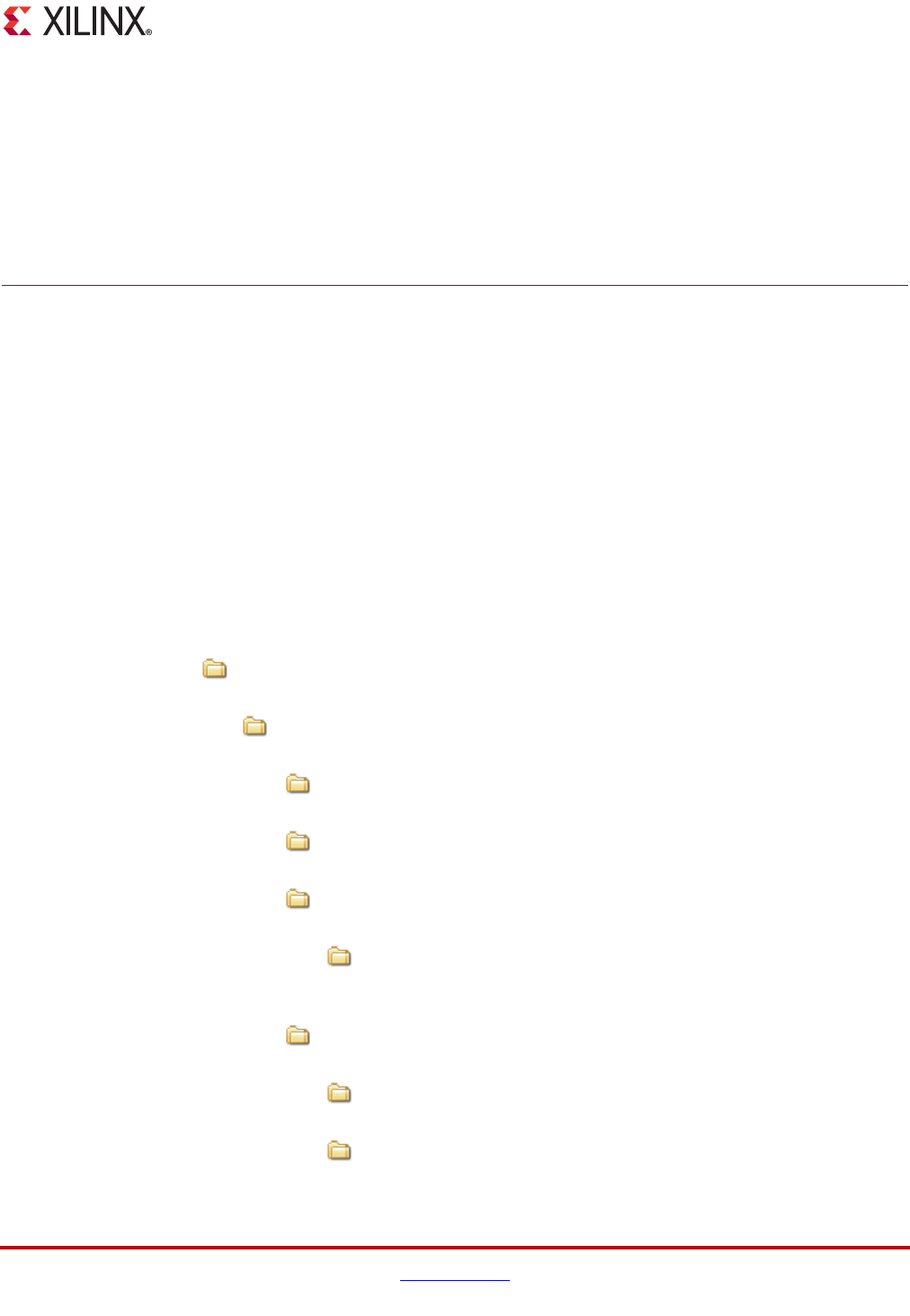

<project directory>

Top-level project directory; name is user-defined.

<project directory>/<component name>

Core release notes file

<component name>/doc

Product documentation

<component name>/example design

Verilog or VHDL design files

<component name>/implement

Implementation script files

implement/results

Results directory, created after implementation scripts are run, and

contains implement script results

<component name>/simulation

Simulation scripts

simulation/functional

Functional simulation files

simulation/timing

Timing simulation files