118 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

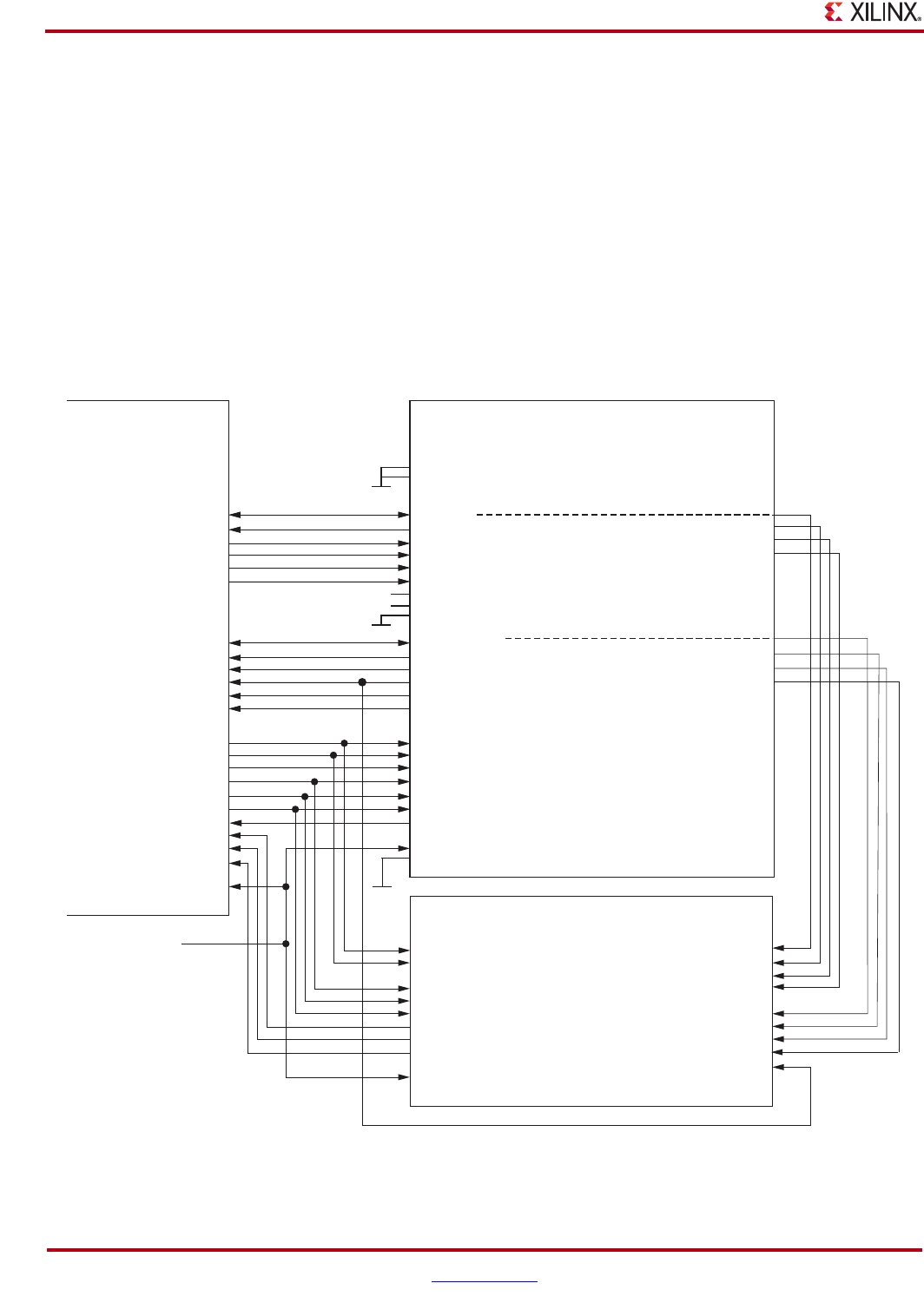

Chapter 12: System Integration

Because the EMAC core can often be used in different clocking modes, note the following:

• The Ethernet transmitter client clock domain must always be connected to the

tx_clk input of the Ethernet AVB Endpoint core. Additionally, the transmitter clock

enable, as used with the EMAC, must always be connected to the tx_clk_en input

of the Ethernet AVB Endpoint core.

• The Ethernet receiver client clock domain must always be connected to the rx_clk

input of the Ethernet AVB Endpoint core. Additionally, the receiver clock enable, as

used with the EMAC, must always be connected to the rx_clk_en input of the

Ethernet AVB Endpoint core.

• The host_clk input of the Ethernet AVB Endpoint and the HOSTCLK input the

EMAC must always share the same clock source.

Connections Including Ethernet Statistics

X-Ref Target - Figure 12-4

Figure 12-4: Connection to the Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC and Ethernet Statistic

Core

tx_clk

tx_clk_en

tx_data[7:0]

tx_data_valid

tx_underrun

tx_ack

rx_clk

rx_clk_en

rx_data[7:0]

rx_data_valid

host_opcode[1:0]

host_addr[9:0]

host_wr_data[31:0]

host_req

host_miim_sel

host_miim_rdy

host_rd_data_mac[31:0]

hos_rd_data_stats[31:0]

host_clk

CLIENTEMAC0PAUSEREQ

CLIENTEMAC0PAUSEVAL[15:0]

TX_CLK_0

TX_CLIENT_CLK_ENABLE_0

CLIENTEMAC0TXD[7:0]

CLIENTEMAC0TXDVLD

CLIENTEMAC0TXUNDERRUN

EMAC0CLIENTTXACK

EMAC0CLIENTTXCOLLISION

EMAC0CLIENTTXRETRANSMIT

CLIENTEMAC0IFGDELAY

GMII_RX_CLK0

RX_CLIENT_CLK_ENABLE_0

EMAC0CLIENTRXD[7:0]

EMAC0CLIENTRXDVLD

EMAC0CLIENTRXGOODFRAME

EMAC0CLIENTRXBADFRAME

HOSTOPCODE[1:0]

HOSTADDR[9:0]

HOSTWRDATA[31:0]

HOSTREQ

HOSTMIIMSEL

HOSTMIIMRDY

HOSTCLK

HOSTEMAC1SEL

EMAC0CLIENTTXSTATS

EMAC0CLIENTTXSTATSVLD

EMAC0CLIENTTXSTATSBYTEVLD

EMAC0CLIENTRXSTATS[6:0]

EMAC0CLIENTRXSTATSVLD

EMAC0CLIENTRXSTATSBYTEVLD

host_clk

GND

GND

NC

NC

GND

host_opcode[1:0]

host_addr[9:0]

host_req

host_miim_sel

host_miim_rdy

host_rd_data[31:0]

host_stats_lsw_rdy

host_stats_msw_rdy

host_clk

txclientclkin

clienttxstats

clienttxstatsvld

clienttxstatsbytevalid

rxclientclkin

clientrxstats[6:0]

clientrxstatsvld

clientrxstatsbyteva

lid

clientrxdvld

host_stats_lsw_rdy

host_stats_msw_rdy

rx_frame_good

rx_frame_bad

Ethernet Statistics Block-level Wrapper

(from Ethernet Statistics Example Design)

Block-level Wrapper

(from Virtex-5 Embedded Tri-mode

Ethernet MAC Wrapper)

Ethernet AVB Endpoint

Core Netlist

HOSTRDDATA[31:0]