Ethernet AVB Endpoint User Guide www.xilinx.com 113

UG492 July 23, 2010

Using the Xilinx LogiCORE IP Tri-Mode Ethernet MACs

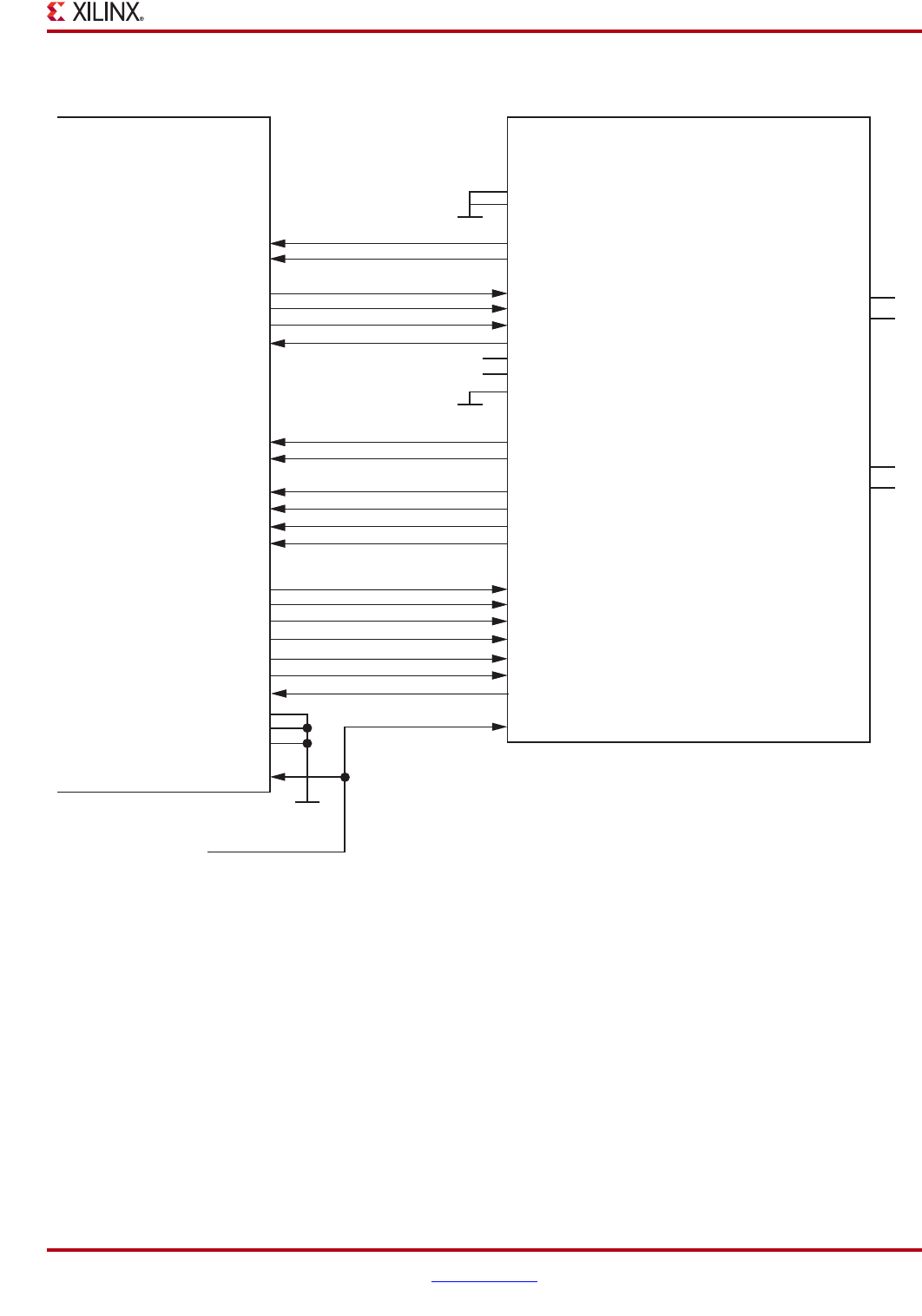

Connections Without Ethernet Statistics

Figure 12-1 illustrates the connection of the Ethernet AVB Endpoint core to the Xilinx Tri-

Mode Ethernet MAC (TEMAC) core when not using the Ethernet Statistics core.

Figure 12-1 provides detail for the connections between the two cores which were shown

in Figure 5-1.

All connections, as shown, are logic-less connections. Because the AVB standard does not

include support for half-duplex or flow control operation, the relevant half-duplex/flow-

control signals of the TEMAC can be left unused: inputs can be tied to logic 0, outputs can

be left unconnected.

X-Ref Target - Figure 12-1

Figure 12-1: Connection to the Tri-Mode Ethernet MAC Core (without Ethernet Statistics)

tx_clk

tx_clk_en

tx_data[7:0]

rx_clk

rx_clk_en

rx_data[7:0]

rx_data_valid

rx_frame_good

rx_frame_bad

host_opcode[1:0]

host_addr[9:0]

host_wr_data[31:0]

host_req

host_miim_sel

host_miim_rdy

host_rd_data_mac[31:0]

host_rd_data_stats[31:0]

host_stats_lsw_rdy

host_sta

ts_msw_rdy

host_clk

pause_req

tx_clk

tx_clk_en

tx_data[7:0]

tx_collision

tx_retransmit

rx_clk

rx_clk_en

rx_data[7:0]

rx_frame_good

rx_data_valid

rx_frame_bad

host_opcode[1:0]

host_addr[9:0]

host_wr_data[31:0]

host_req

host_miim_sel

host_miim_rdy

host_rd_data[31:0]

host_clk

host_clk

NC

NC

NC

NC

GND

NC

NC

GND

GND

tx_data_valid

tx_underrun

tx_ack

tx_data_valid

tx_underrun

tx_ack

tx_ifg_delay[7:0]

pause_val[15:0]

rx_statistics_valid

tx_statistics_vector[31:0]

rx_statistics_vector[27:0]

tx_statistics_valid

TEMAC Block-level Wrapper

(from TEMAC Example Design)

Ethernet AVB Endpoint

Core Netlist