98 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Chapter 10: Configuration and Status

MAC Header Filter Configuration

When the core is generated in “EDK pcore Format”, the “Legacy MAC Header Filters” are

not included since the xps_ll_temac can optionally contain its own Address Filter logic.

When not provided, the following address locations will return 0s for a read and all writes

will be ignored.

When the core is generated in “Standard CORE Generator Format”, the “Legacy MAC

Header Filters” are provided. These filters are present on the Rx Legacy traffic path, are

capable of providing match recognition logic against eight unique MAC frame headers.

Each of the eight individual filters require eight memory mapped registers to configure

them, as defined in Table 10-16. Each individual filter contains its own set of these eight

registers. When interpreting Table 10-16, the variable filter# should be replaced with an

integer number between 0 and 7, which represent the eight individual filters.

3 0 WO PTP Receiver logic reset. When written with a '1',

forces the PTP receiver logic of the core to be reset.

This is a subset of the full receiver path reset of bit 1.

This reset does not affect PTP receiver configuration

settings.

If read, always returns 0.

31-4 0 RO Unused

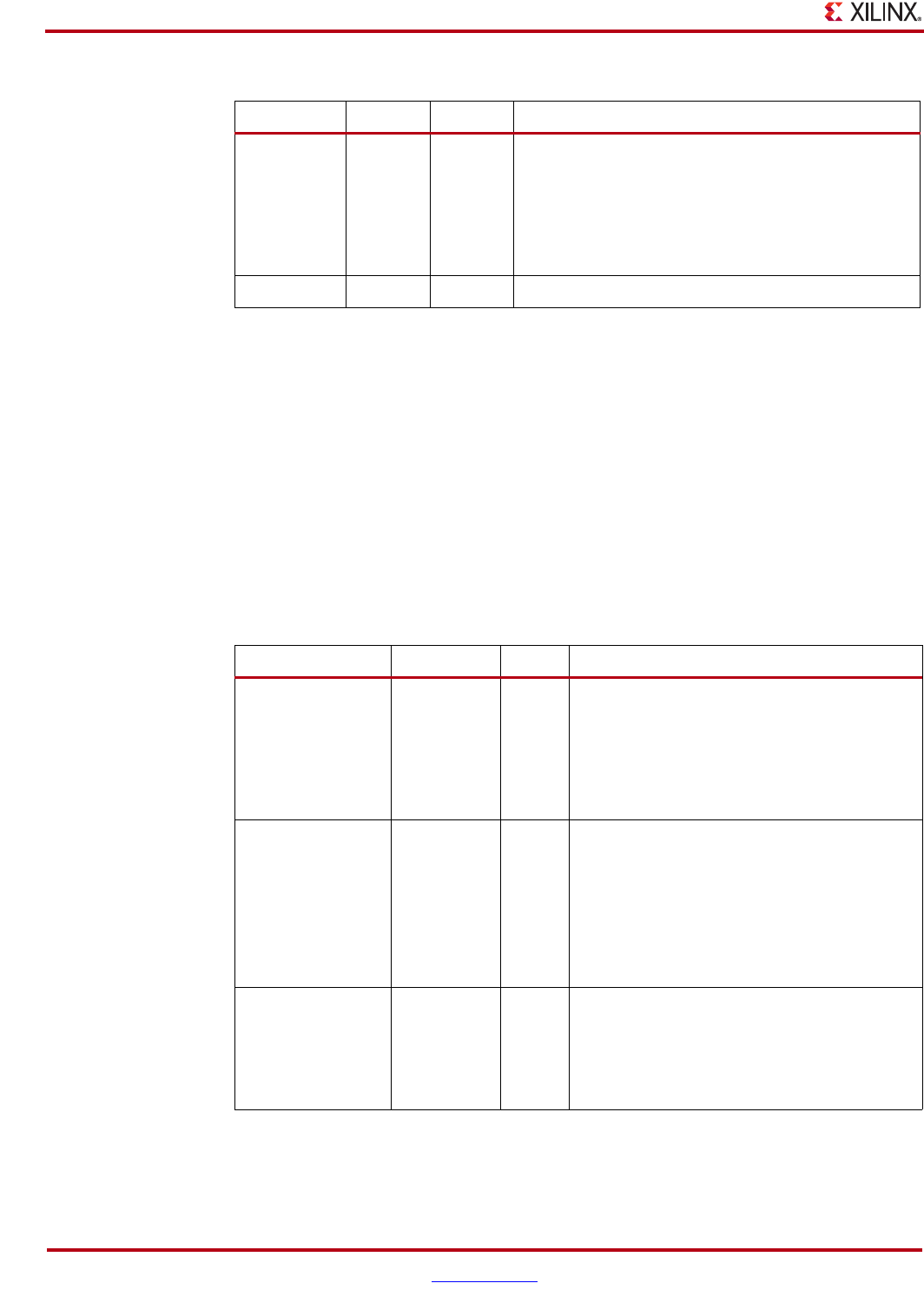

Table 10-15: Software Reset Register (Address at PLB_base_address + 0x2828)

Bit Number Default Access Description

Table 10-16: MAC Header Filter Configuration Registers

Address Default Access Description

PLB_base_address

+ 0x3000

+ (filter# * 0x20)

+ 0x0

0xFFFFFFFF R/W Match Pattern: Ethernet frame bits 0 to 31

32 bit pattern to match against the Ethernet

frame bits 0 to 31. Specifically, match pattern

bits:

[31:0]: MAC Destination Address Field bits

[31:0]

PLB_base_address

+ 0x3000

+ (filter# * 0x20)

+ 0x4

0x0000FFFF R/W Match Pattern: Ethernet frame bits 32 to 63

32 bit pattern to match against the Ethernet

frame bits 32 to 63. Specifically, match pattern

bits:

[15:0]: MAC Destination Address Field bits

[47:32]

[31:16]: MAC Source Address Field bits [15:0]

PLB_base_address

+ 0x3000

+ (filter# * 0x20)

+ 0x8

0x00000000 R/W Match Pattern: Ethernet frame bits 64 to 95

32 bit pattern to match against the Ethernet

frame bits 64 to 95. Specifically, match pattern

bits:

[31:0]: MAC Source Address bits [47:16]