Ethernet AVB Endpoint User Guide www.xilinx.com 93

UG492 July 23, 2010

PLB Address Map and Register Definitions

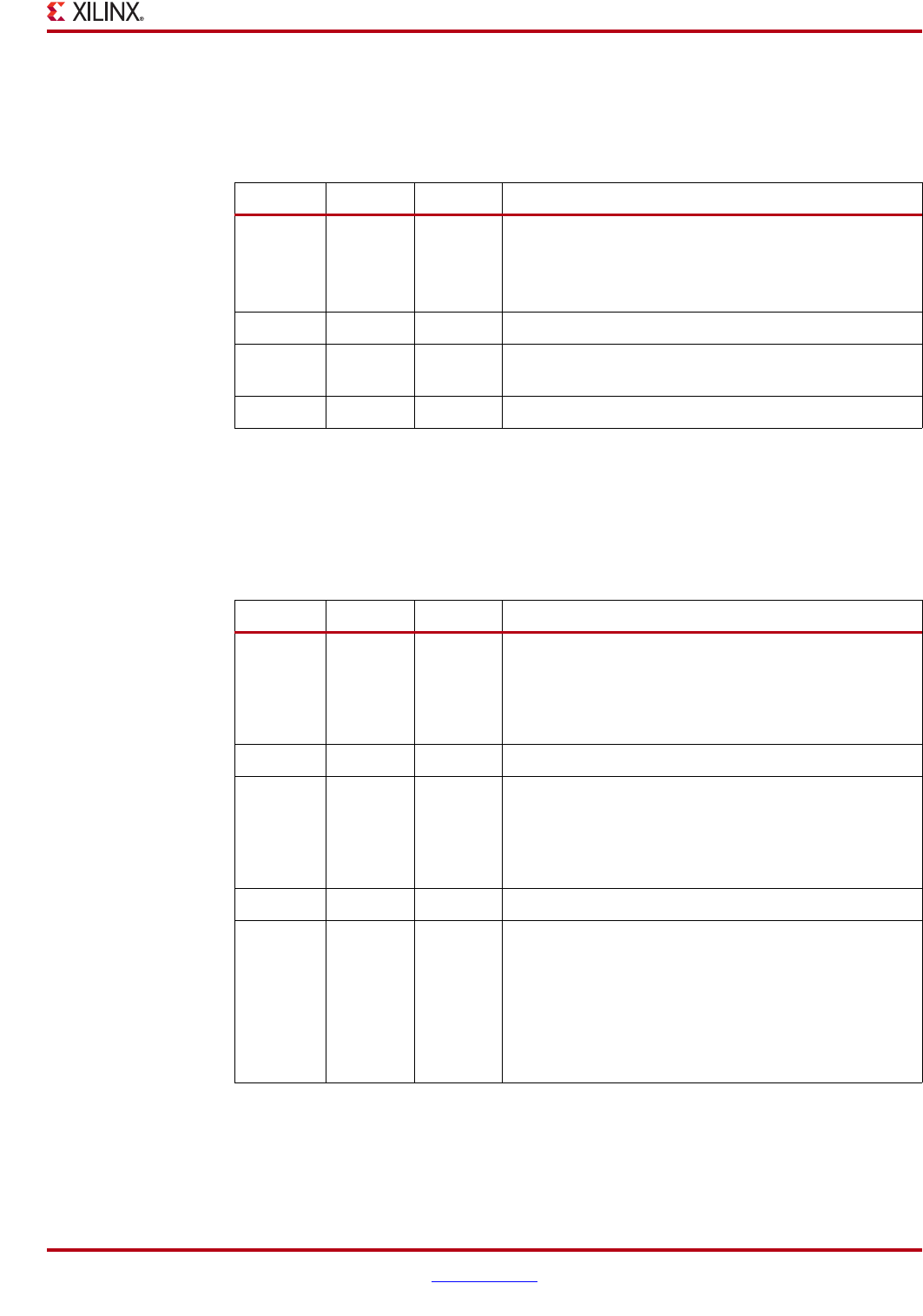

Rx PTP Packet Control Register

Table 10-2 defines the associated control register of the “Rx PTP Packet Buffer,” used by

the “Software Drivers” to monitor the position of the most recently received PTP frame.:

Rx Filtering Control Register

Table 10-3 defines the associated control register of the “Rx Splitter.” The Rx path is

capable of identifying the AV packets using configurable VLAN priority:

Table 10-2: Rx PTP Packet Buffer Control Register (PLB_base_address + 0x2004)

Bit no Default Access Description

00WOrx_clear. When written with a ‘1,’ forces the buffer to

empty, in practice moving the write address to the same

value as the read address.

If read, always return 0.

7-1 0 RO Unused

11-8 0 RO rx_packet. Indicates the number (block RAM bin

position) of the most recently received PTP packet.

31-12 0 RO Unused

Note: A read or a write to this register clears the interrupt_ptp_rx interrupt (asserted after each

successful PTP packet reception).

Table 10-3: Rx Filtering Control Register (PLB_base_address + 0x2008)

Bit no Default Access Description

2-0 3 R/W VLAN Priority A. If a tagged packet is received with a

VLAN priority field matching either of the Priority A or

B values, then the packet will be considered as an AV

frame: it will be passed to the AV I/F. Otherwise it will

be passed to the Legacy I/F.

7-3 0 RO Unused

10-8 2 R/W VLAN Priority B. If a tagged packet is received with a

VLAN priority field matching either of the Priority A or

B values, then the packet will be considered as an AV

frame: it will be passed to the AV I/F. Otherwise it will

be passed to the Legacy I/F.

15-11 0 RO Unused

16 1 R/W Promiscuous Mode for the

“Legacy MAC Header

Filters.”

If this bit is set to 1, the MAC Header Filter is set to

operate in promiscuous mode. All frames will be passed

to the

“Rx Legacy Traffic I/F.”

If set to 0 then only matching MAC headers are passed

to the

“Rx Legacy Traffic I/F.”