96 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Chapter 10: Configuration and Status

This register and the registers defined in Table 10-11 and in Table 10-12 are linked. When

this nanoseconds value register is read, the entire RTC (including the seconds field) is

sampled.

Table 10-11 describes the lower 32-bits of the seconds value register for the seconds field of

the “Real Time Clock.” When read, this returns the latest value of the counter.

This register and the registers defined in Table 10-10 and in Table 10-12 are linked. When

the nanoseconds value register is read (see Table 10-10), the entire RTC is sampled.

Table 10-12 describes the upper 16-bits of the seconds value register for the seconds field of

the “Real Time Clock.” When read, this returns the latest value of the counter.

This register and the registers defined in Table 10-10 and in Table 10-11 are linked. When

the nanoseconds value register is read (see Table 10-10), the entire RTC is sampled.

RTC Interrupt Clear Register

Table 10-13 describes the control register defined for the interrupt_ptp_timer signal,

the periodic interrupt signal which is raised by the “Real Time Clock.”

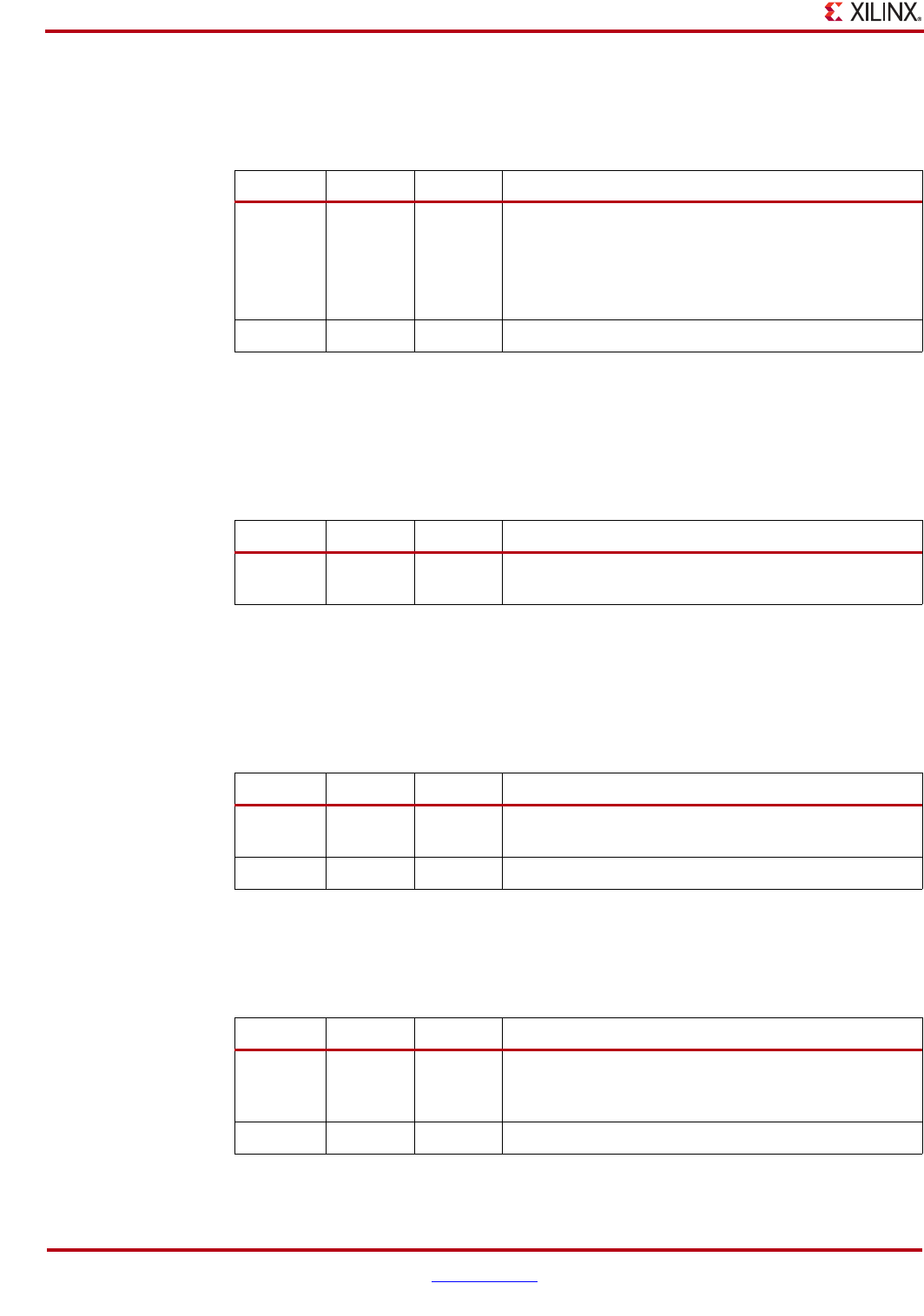

Table 10-10: Current RTC Nanoseconds Value (

PLB_base_address + 0x2814)

Bit no Default Access Description

29-0 0 RO Current Value of the synchronized RTC nanoseconds

field.

Note: A read from this register samples the entire RTC

counter (synchronized) so that the Epoch and Seconds

field are held static for a subsequent read.

31-30 0 RO Unused

Table 10-11: Current RTC Seconds Field Value bits [31:0] (PLB_base_address +

0x2818)

Bit no Default Access Description

31-0 0 RO Sampled Value of the synchronized RTC Seconds field

(bits 31-0).

Table 10-12: Current RTC Seconds Field Value bits [47:32] (PLB_base_address +

0x281C)

Bit no Default Access Description

15-0 0 RO Sampled Value of the synchronized RTC Seconds field

(bits 47-32).

32-16 0 RO Unused

Table 10-13: RTC Interrupt Clear Register (PLB_base_address + 0x2820)

Bit no Default Access Description

0 0 WO Write ANY value to bit 0 of this register to clear the

interrupt_ptp_timer Interrupt signal. This bit always

returns 0 on read.

31-1 0 RO Unused