Ethernet AVB Endpoint User Guide www.xilinx.com 99

UG492 July 23, 2010

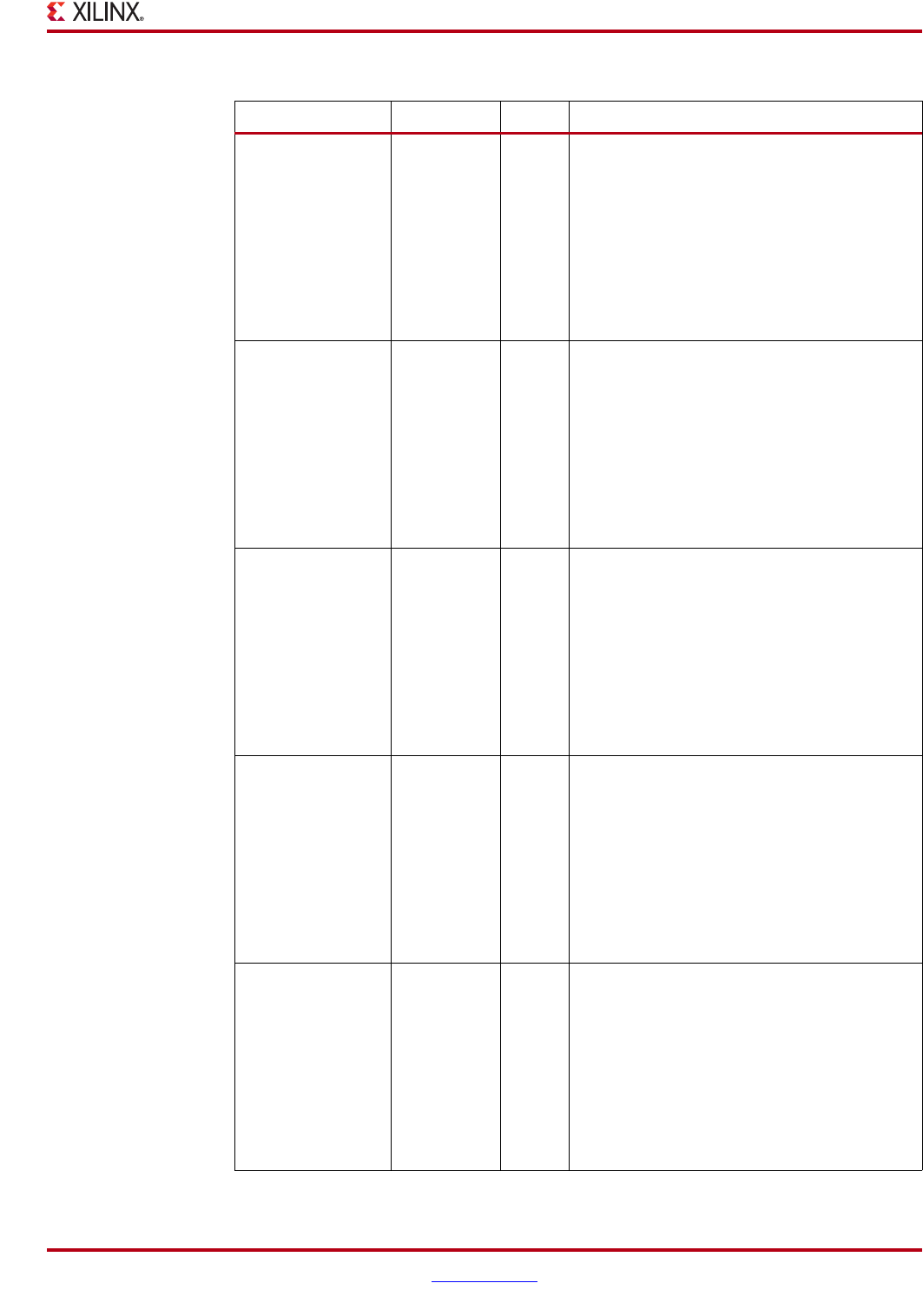

PLB Address Map and Register Definitions

PLB_base_address

+ 0x3000

+ (filter# * 0x20)

+ 0xC

0x00000000 R/W Match Pattern: Ethernet frame bits 96 to 127

32 bit pattern to match against the Ethernet

frame bits 96 to 127.

For frames with a VLAN tag, match pattern

bits[31:0] can be matched against the full

VLAN field.

For frames without a VLAN, match pattern

bits[15:0] can be matched against the

Length/Type field.

PLB_base_address

+ 0x3000

+ (filter# * 0x20)

+ 0x10

0xFFFFFFFF R/W Match Enable: Ethernet frame bits 0 to 31

There is a 1-to-1 correspondence between all

bits in this register and all bits in the "Match

Pattern: Ethernet frame bits 0 to 31" register.

For each bit:

logic 1 enables the match: the corresponding

bit in the Match Pattern will be compared

logic 0 disables the match: the corresponding

bit in the Match Pattern will be a don’t-care.

PLB_base_address

+ 0x3000

+ (filter# * 0x20)

+ 0x14

0x0000FFFF R/W Match Enable: Ethernet frame bits 32 to 63

There is a 1-to-1 correspondence between all

bits in this register and all bits in the "Match

Pattern: Ethernet frame bits 32 to 63" register.

For each bit:

logic 1 enables the match: the corresponding

bit in the Match Pattern will be compared

logic 0 disables the match: the corresponding

bit in the Match Pattern will be a don’t-care.

PLB_base_address

+ 0x3000

+ (filter# * 0x20)

+ 0x18

0x00000000 R/W Match Enable: Ethernet frame bits 64 to 95

There is a 1-to-1 correspondence between all

bits in this register and all bits in the "Match

Pattern: Ethernet frame bits 64 to 95" register.

For each bit:

logic 1 enables the match: the corresponding

bit in the Match Pattern will be compared

logic 0 disables the match: the corresponding

bit in the Match Pattern will be a don’t-care.

PLB_base_address

+ 0x3000

+ (filter# * 0x20)

+ 0x1C

0x00000000 R/W Match Enable: Ethernet frame bits 96 to 127

There is a 1-to-1 correspondence between all

bits in this register and all bits in the "Match

Pattern: Ethernet frame bits 96 to 127" register.

For each bit:

logic 1 enables the match: the corresponding

bit in the Match Pattern will be compared

logic 0 disables the match: the corresponding

bit in the Match Pattern will be a don’t-care.

Table 10-16: MAC Header Filter Configuration Registers (Cont’d)

Address Default Access Description