Ethernet AVB Endpoint User Guide www.xilinx.com 159

UG492 July 23, 2010

Chapter 16

Detailed Example Design (EDK format)

This chapter provides detailed information about the core when generated in the Standard

Embedded Development Kit (EDK) format, including a description of files and the

directory structure generated. This option is selected from page 1 of the customization

GUI.

Please refer instead to Chapter 15, “Detailed Example Design (Standard Format).” when

requiring the Standard CORE Generator™ software format.

top directory link - white tex t invisible

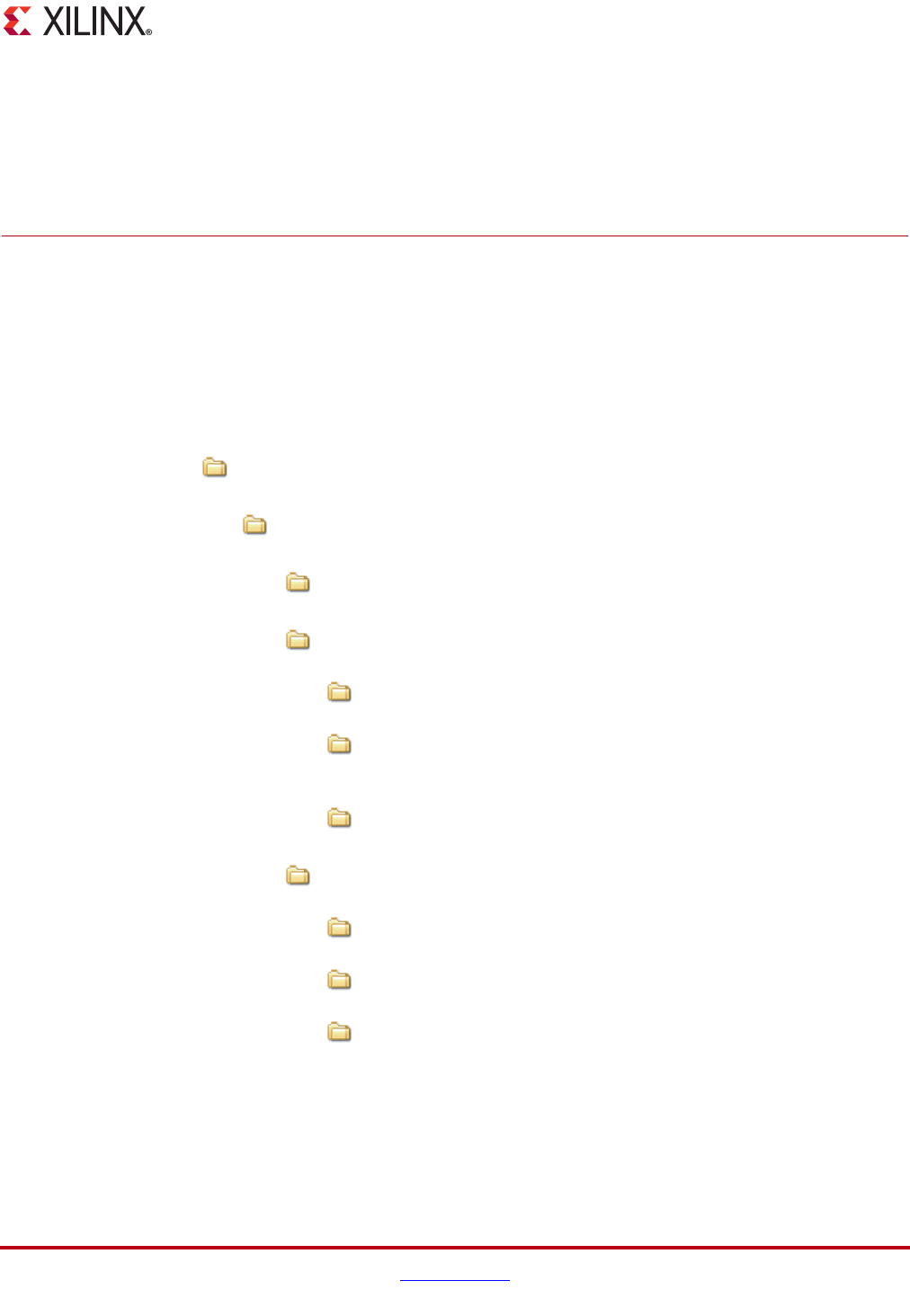

<project directory>

Top-level project directory; name is user-defined.

<project directory>/<component name>

Core release notes file

<component name>/doc

Product documentation

MyProcessorIPLib/pcores/eth_avb_endpoint_v2_04_a

core netlist and HDL for the pcore

pcores/eth_avb_endpoint_v2_04_a/data

Data files for automatic integration into Xilinx Platform Studio

pcores/eth_avb_endpoint_v2_04_a/hdl/vhdl

VHDL wrapper file for the core netlist to enable integration into

Platform Studio

pcores/eth_avb_endpoint_v2_04_a/netlist

The Ethernet AVB Endpoint core netlist

MyProcessorIPLib/drivers/avb_v2_04_a

Software Device Drivers for the pcore

drivers/avb_v2_04_a/data

Data files for automatic integration into Xilinx Platform Studio

drivers/avb_v2_04_a/examples

An application example using the low-level driver files

drivers/avb_v2_04_a/src

Low-level driver source C files