156 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Chapter 15: Detailed Example Design (Standard Format)

Demonstration Test Bench

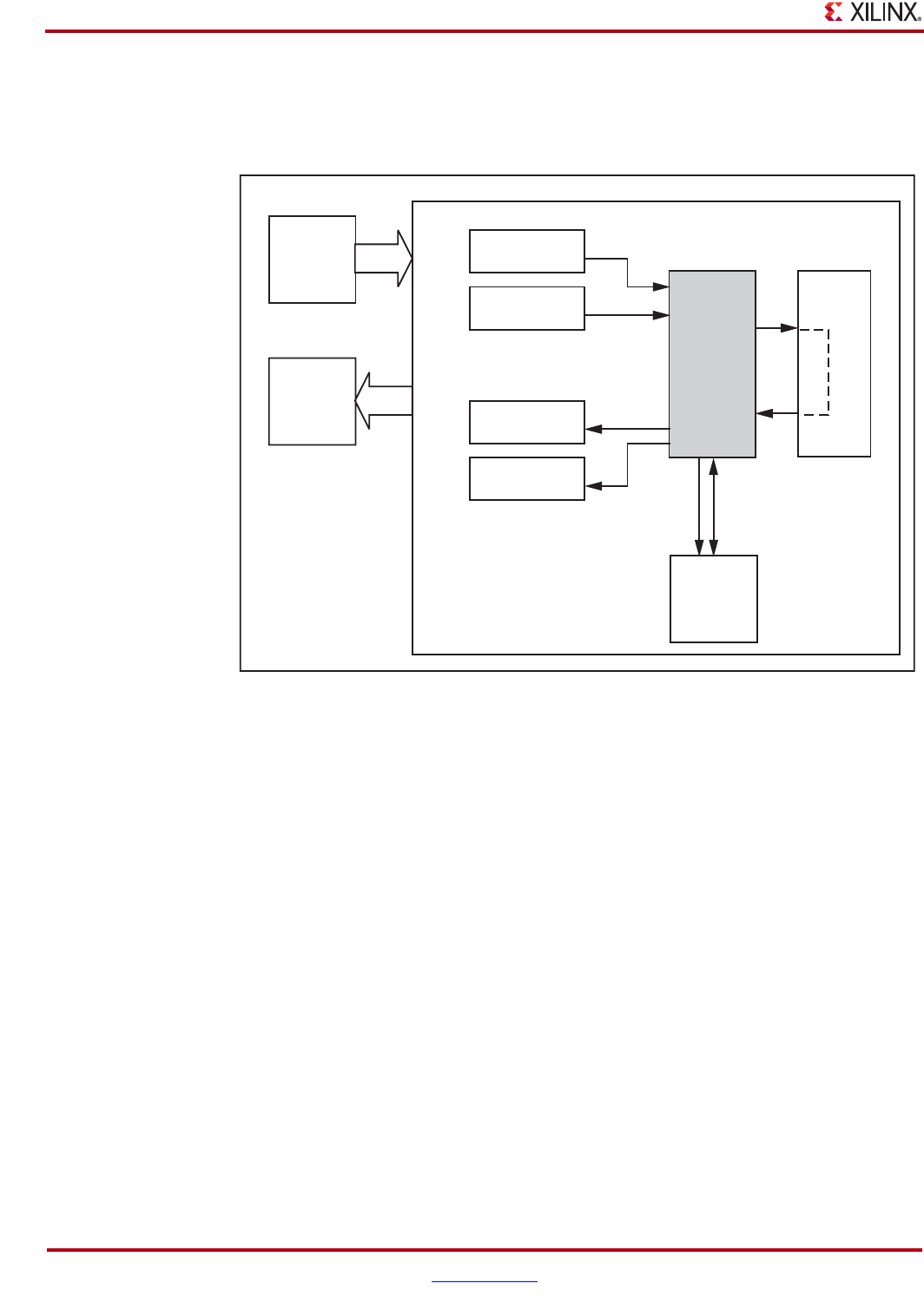

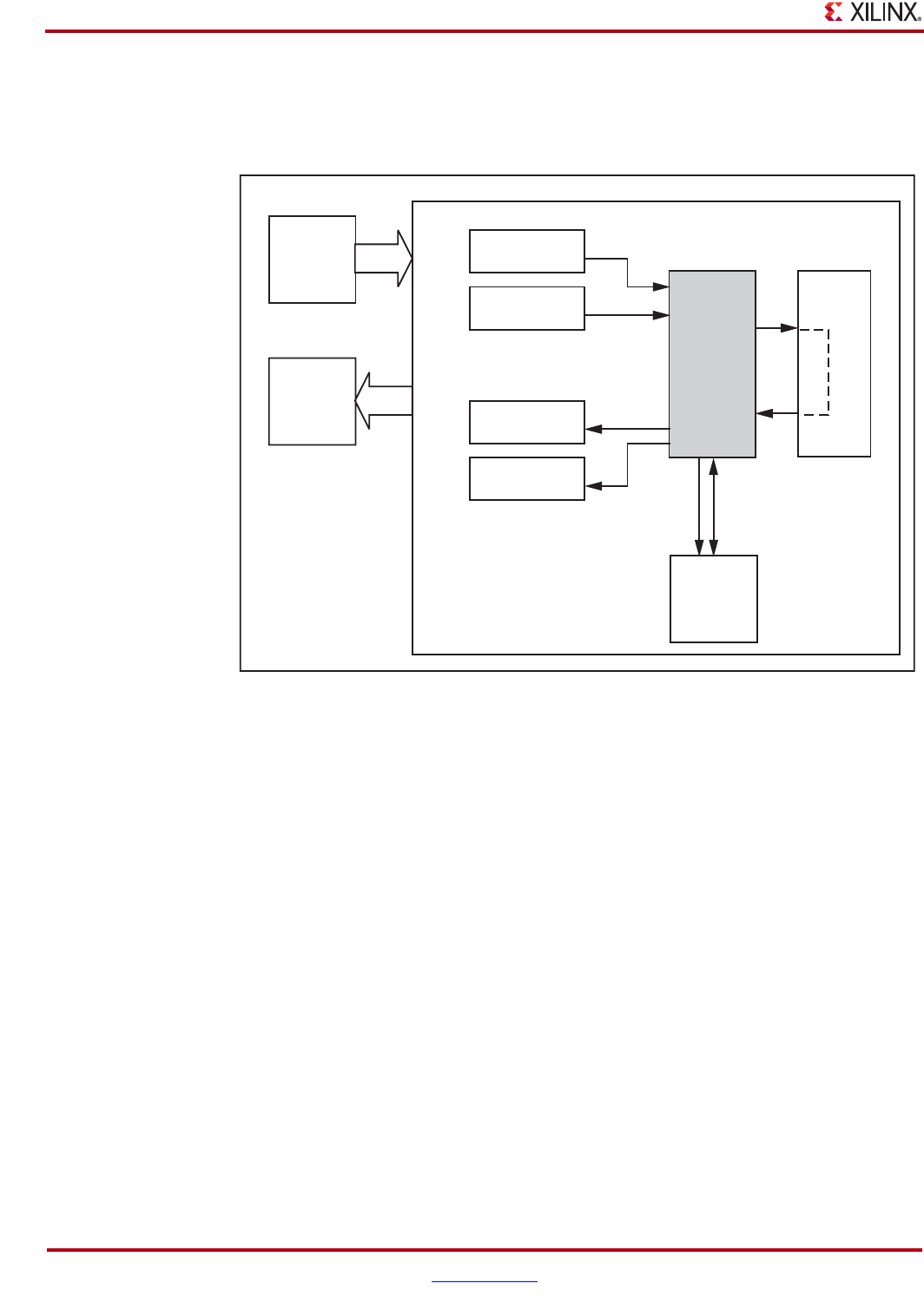

Figure 15-2 illustrates the Ethernet AVB Endpoint demonstration test bench, a simple

VHDL or Verilog program for exercising the example design and the core.

The following files describe the top level of the demonstration test bench:

VHDL

<project_dir>/<component_name>/simulation/demo_tb.vhd

Verilog

<project_dir>/<component_name>/simulation/demo_tb.v

The top-level test bench entity instantiates the example design for the core, which is the

Device Under Test (DUT). The test bench provides clocks and resets, and gathers statistics

for the duration of the simulation. A final statistic report is created at the end of the

simulation run time that contains the following:

• The number of PTP frames transmitted and received

• The number of AV frames transmitted and received

• The number of legacy frames transmitted and received.

All transmitted frame statistics should exactly match the received frame statistics for

each particular frame type; if this is not the case, an error message is issued.

• Finally, the test bench estimates the percentage of overall Ethernet line rate consumed

by each of the three types. This should illustrate the bandwidth policing functionality

of the core, which should only allow the AV frames to consume a maximum of 75% of

the overall bandwidth.

X-Ref Target - Figure 15-2

Figure 15-2: Ethernet AVB Endpoint Demonstration Test Bench

Example Design Top Level

Ethernet

AVB

Endpoint

LogiCORE

legacy

traffic

AV trafficTx frame

stimulus

loopback

module

Tx frame

stimulus

Rx frame

checker

Rx frame

checker

PLBInterrupts

PLB

module

AV traffic

legacy

traffic

Clock

and

Reset

generation

Statistic

Gathering

Demonstration Test Bench