18 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Preface: About This Guide

• Chapter 13, “Software Drivers” describes the function of the software drivers

delivered with the core.

• Chapter 14, “Quick Start Example Design”Chapter 3, “Quick Start Example Design”

provides instructions to quickly generate the core and run the example design

through implementation and simulation using the default settings.

• Chapter 15, “Detailed Example Design (Standard Format)” provides detailed

information about the core when generated in the standard CORE Generator format,

including a description of files and the directory structure generated

• Chapter 16, “Detailed Example Design (EDK format)” provides detailed information

about the core when generated in the Standard Embedded Development Kit (EDK)

format, including a description of files and the directory structure generated.

• Appendix A, “RTC Time Stamp Accuracy” describe the necessity of accurate time

stamps, essential to the Precise Timing Protocol across the network link, and provides

some of the ways inaccuracies are introduced.

Conventions

This document uses the following conventions. An example illustrates each convention.

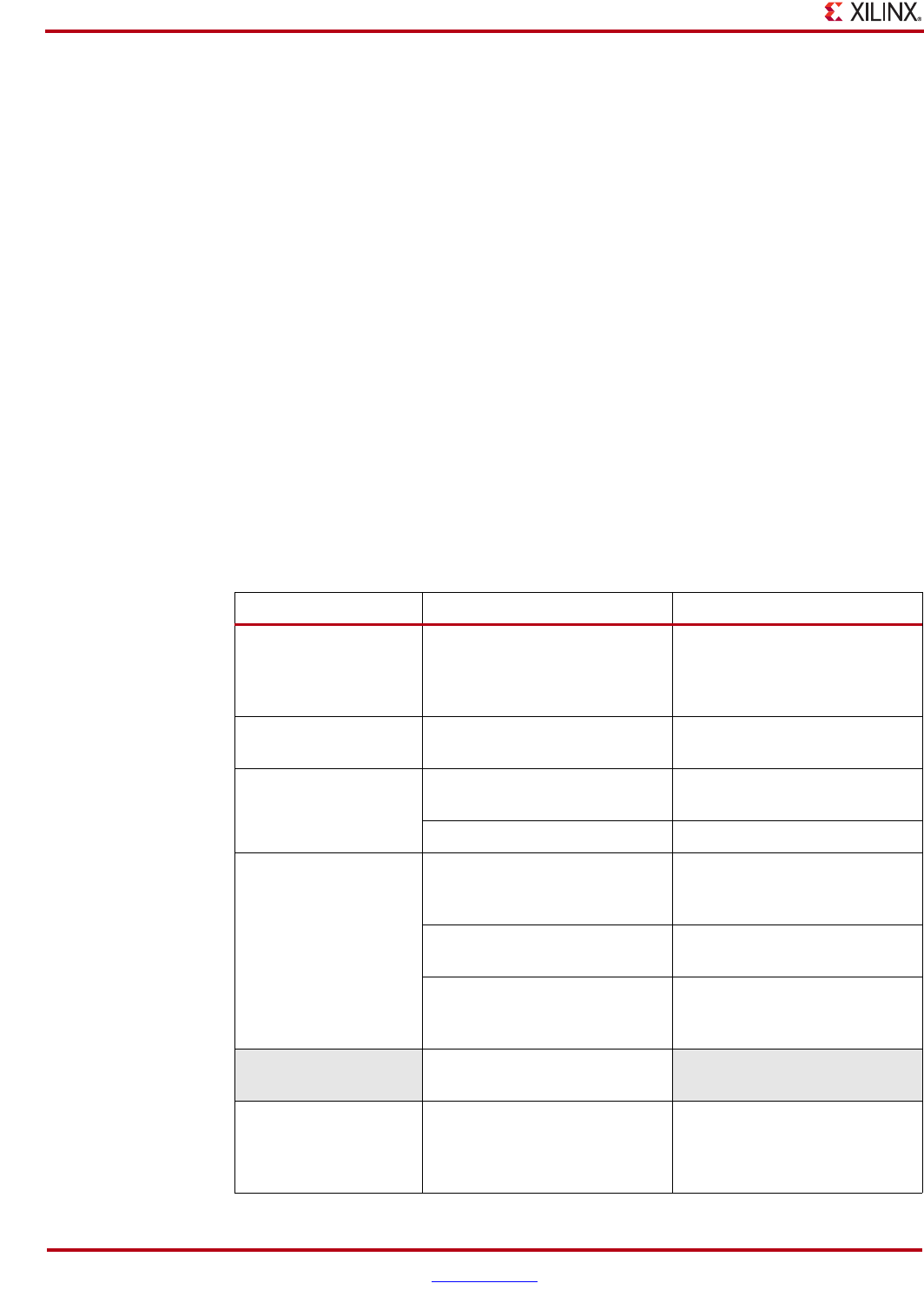

Typographical

The following typographical conventions are used in this document:

Convention Meaning or Use Example

Courier font

Messages, prompts, and

program files that the system

displays. Signal names in text

also.

speed grade: - 100

Courier bold

Literal commands that you enter

in a syntactical statement

ngdbuild design_name

Helvetica bold

Commands that you select from

a menu

File → Open

Keyboard shortcuts Ctrl+C

Italic font

Variables in a syntax statement

for which you must supply

values

ngdbuild design_name

References to other manuals

See the User Guide for more

information.

Emphasis in text

If a wire is drawn so that it

overlaps the pin of a symbol, the

two nets are not connected.

Dark Shading

Items that are not supported or

reserved

This feature is not supported

Square brackets [ ]

An optional entry or parameter.

However, in bus specifications,

such as bus[7:0], they are

required.

ngdbuild [option_name]

design_name