80 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Chapter 8: Real Time Clock and Time Stamping

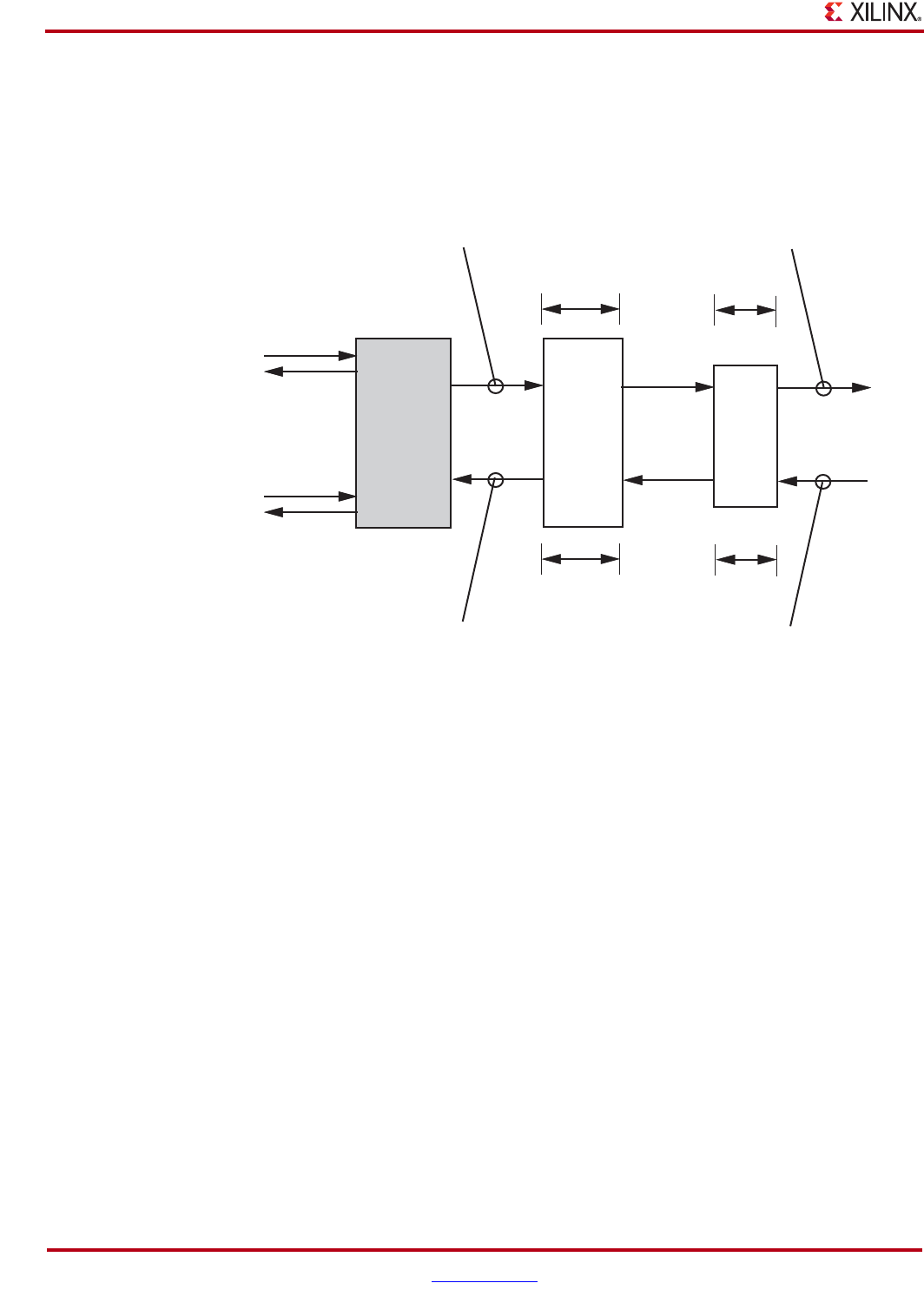

Time Stamp Sampling Position of MAC Frames

A time stamp value should be sampled at the beginning of the first symbol following the

Start of Frame Delimiter (SFD) of the Ethernet MAC frame as seen on the PHY. This is

illustrated in Figure 8-3.

Figure 8-3 also illustrates the actual time stamp sampling position that is used by the core.

Time stamps are taken after the MAC frame SFD is seen not on the GMII, but on the MAC

Client I/F. The time stamping logic is deliberately designed this way for the following

reasons:

1. When the Ethernet AVB Endpoint core is to be connected to the Embedded Tri-Mode

Ethernet MAC, the GMII is not always available to the FPGA fabric logic: specifically

when used with a 1000BASE-X or SGMII physical interface, the GMII exists only as an

internal connection within the embedded block. Therefore, by sampling on the client

interface, we enable the Ethernet AVB Endpoint core to be connected to ANY Xilinx

Tri-Mode MAC used in ANY configuration.

2. Sampling on the MAC Client I/F provides the Ethernet AVB Endpoint core with the

required time stamp exactly when it is needed. Sampling on the GMII would require

the use of sideband Time stamp Value FIFOs (there may be more than a single MAC

frame present in the pipeline stages of the MAC transmitter or receiver). So by

sampling on the MAC Client I/F, we are also able to reduce the need for extra FIFO

logic.

X-Ref Target - Figure 8-3

Figure 8-3: Time Stamping Position

Tri-Mode

Ethernet

MAC

LogiCORE

Ethernet

AVB

Endpoint

LogiCORE

legacy

traffic

AV

traffic

Ethernet

PHY

GMII

MAC

Client I/F

Tx

Tx

Rx Rx

PHY Media

IEEE defined Tx

sample position

IEEE defined Rx

sample position

Xilinx Rx

sample position

Xilinx Tx

sample position

known fixed

Tx latency

known fixed

Rx latency

PHY-specific

Tx latency

PHY-specific

Rx latency