Ethernet AVB Endpoint User Guide www.xilinx.com 119

UG492 July 23, 2010

Using the Xilinx LogiCORE IP Tri-Mode Ethernet MACs

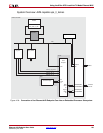

Figure 12-4 illustrates the connection of the Ethernet AVB Endpoint core to the EMAC

when using the Ethernet Statistics core. This shares much in common with Figure 12-2;

however, note the following additional points:

• All of the “MAC Management Interface” output signals of the Ethernet AVB Endpoint

core connect directly to the signals of both the EMAC and Ethernet Statistics cores.

• The Ethernet AVB Endpoint core provides two separate “MAC Management

Interface” inputs for management reads. This allows for logic-less connections

between all three cores as illustrated. To achieve this

♦ connect host_rd_data_mac[31:0] of the Ethernet AVB Endpoint core to the

HOSTRDDATA[31:0] port of the EMAC.

connect host_rd_data_stats[31:0] of the Ethernet AVB Endpoint core to the

host_rd_data[31:0] port of the Ethernet Statistics core.

Virtex-6 FPGA Embedded Tri-Mode Ethernet MAC

The Ethernet AVB Endpoint core will also connect directly to the Virtex-6 FPGA

Embedded Tri-Mode Ethernet MAC (EMAC). Use all of the preceding steps described for

the Virtex-5 FPGA EMAC, the only difference being that Virtex-6 FPGA EMAC does not

come in pairs; each EMAC is an individual element.

Connection of the PLB to the EDK for LogiCORE IP Ethernet MACs

Figure 12-5 illustrates the connection of the core to an embedded processor subsystem

(MicroBlaze™ processor is illustrated). As shown:

• The PLB can be shared across all peripherals as illustrated.

• The “Interrupt Signals” should be connected to the inputs of an interrupt controller

module, for example, the xps_intc core provided with the EDK.

• The embedded processor should be configured to use the software drivers provided

with the core (see Chapter 13, “Software Drivers”) (not illustrated).