Ethernet AVB Endpoint User Guide www.xilinx.com 53

UG492 July 23, 2010

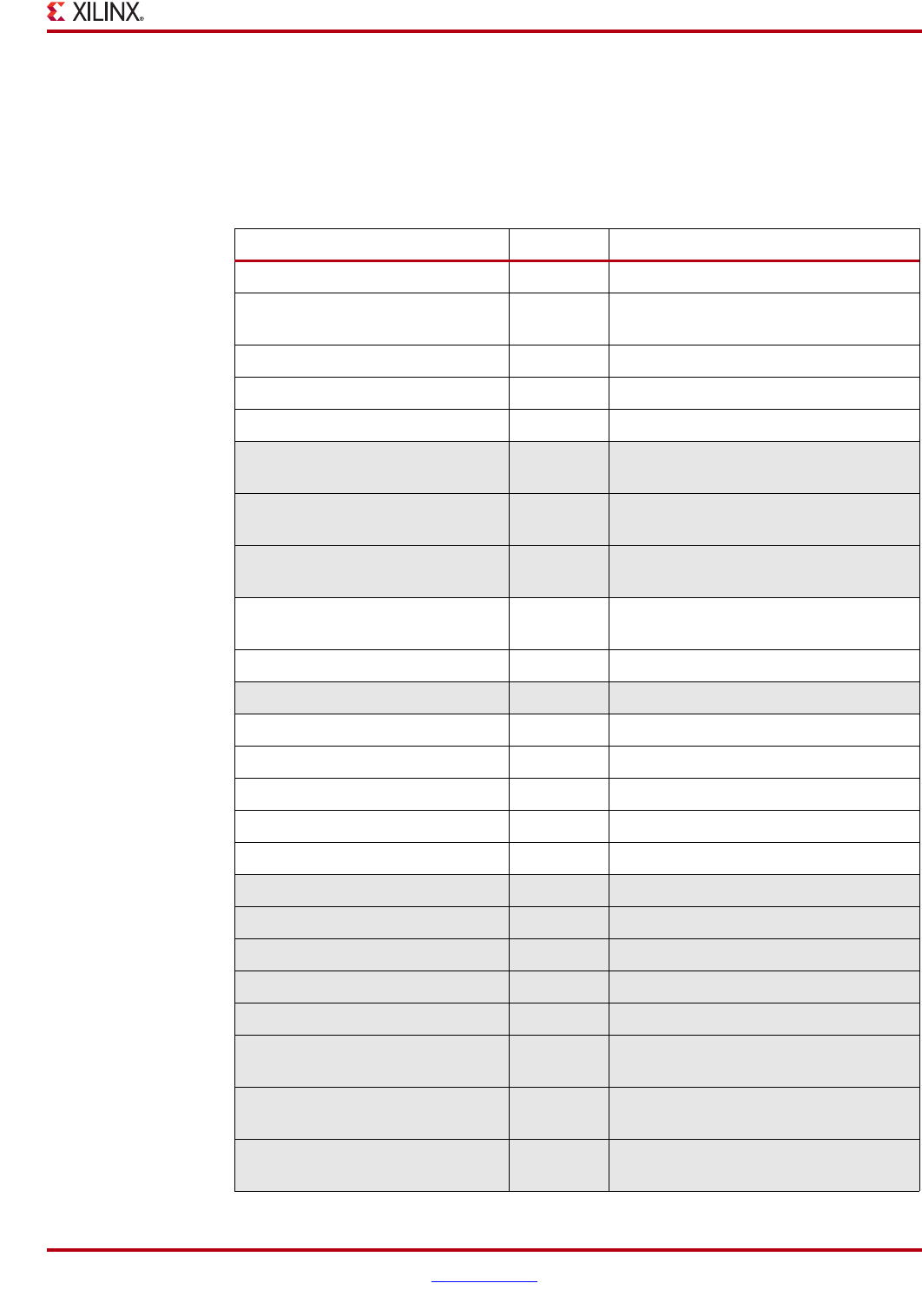

Core Interfaces

PLB Interface

Table 5-9 defines the signals on the PLB bus. For detailed information, see the IBM PLB

specification. Shaded rows represent signals not used by this core; inputs are ignored and

outputs are tied to a constant. These signals are synchronous to PLB_clk; see “Clocks and

Resets” for additional information.

Table 5-9: PLB Signals

PIN Name Direction Description

PLB_clk Input Reference clock for the PLB

PLB_reset Input Reset for the PLB, synchronous to

PLB_clk

PLB_ABus[0:31] input PLB address bus

PLB_UABus[0:31] Input PLB upper address bus

PLB_PAvaild Input PLB primary address valid indicator

PLB_SAValid Input Unused. PLB secondary address valid

indicator.

PLB_rdPrim Input Unused. PLB secondary to primary read

request indicator.

PLB_wrPrim Input Unused. PLB secondary to primary write

request indicator.

PLB_masterID

[0:log2(NUM_MASTERS)]

Input PLB current master identifier

PLB_abort Input PLB abort request indicator

PLB_busLock Input Unused. PLB bus lock.

PLB_RNW Input PLB read not write

PLB_BE[0:3] Input PLB byte enables

PLB_MSize[0:1] Input PLB master data bus size

PLB_size[0:3] Input PLB transfer size. Only support size 0.

PLB_type[0:2] Input PLB transfer type. Only support type 0.

PLB_TAttribute[0:15] Input Unused. PLB transfer attribute bus.

PLB_lockErr Input Unused. PLB lock error indicator.

PLB_wrDBus[0:31] Input PLB write data bus

PLB_wrBurst Input PLB write burst transfer indicator.

PLB_rdBurst Input PLB read burst transfer indicator.

PLB_rdPendReq Input Unused. PLB pending read request

priority.

PLB_wrPendReq Input Unused. PLB pending write request

priority.

PLB_rdPendPri[0:1] Input Unused. PLB pending read bus request

indicator.