48 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Chapter 5: Core Architecture

Legacy Traffic Interface

Legacy Traffic Transmitter Path Signals

Table 5-2 defines the core client-side legacy traffic transmitter signals. These signals are

used to transmit data from the legacy client logic into the core. All signals are synchronous

to the MAC transmitter clock, tx_clk, which must be qualified by the corresponding

clock enable, tx_clk_en (see “Clocks and Resets”).

Legacy Traffic Receiver Path Signals

Table 5-3 defines the core client side legacy traffic receiver signals. These signals are used

by the core to transfer data to the client. All signals are synchronous to the MAC receiver

clock, rx_clk, which must be qualified by the corresponding clock enable, rx_clk_en

(see “Clocks and Resets”).

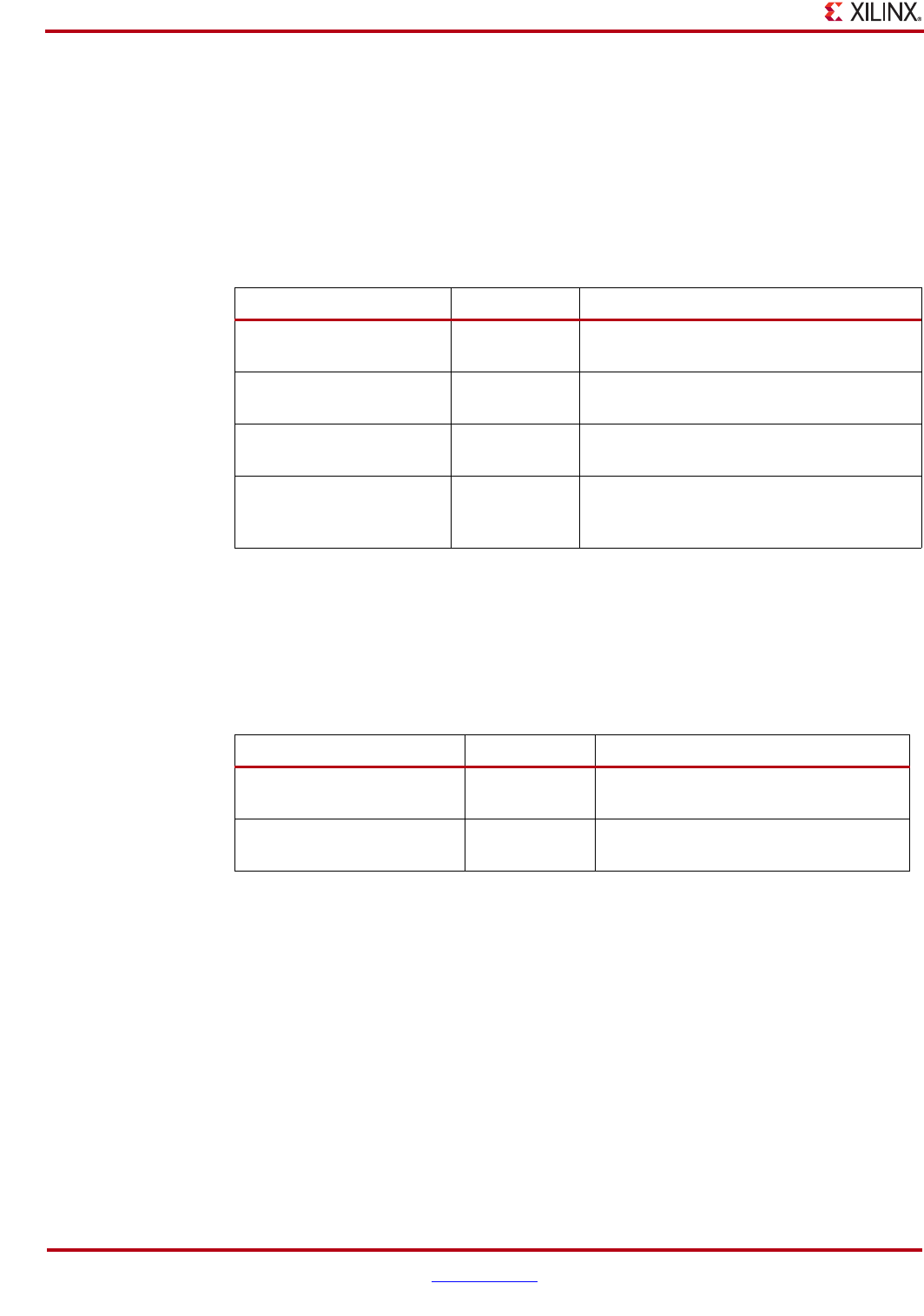

Table 5-2: Legacy Traffic Signals: Transmitter Path

Signal Direction Description

legacy_tx_data[7:0] Input Frame data to be transmitted is supplied on

this port

legacy_tx_data_valid Input A data valid control signal for data on the

legacy_tx_data[7:0] port

legacy_tx_underrun Input Asserted by the client to force the MAC to

corrupt the current frame

legacy_tx_ack Output Handshaking signal asserted when the

current data on legacy_tx_data[7:0]

has been accepted.

Table 5-3: Legacy Traffic Signals: Receiver Path

Signal Direction Description

legacy_rx_data[7:0] Output Legacy frame data received is supplied

on this port.

legacy_rx_data_valid Output Control signal for the

legacy_rx_data[7:0] port