40 www.xilinx.com Ethernet AVB Endpoint User Guide

UG492 July 23, 2010

Chapter 5: Core Architecture

Standard CORE Generator Format

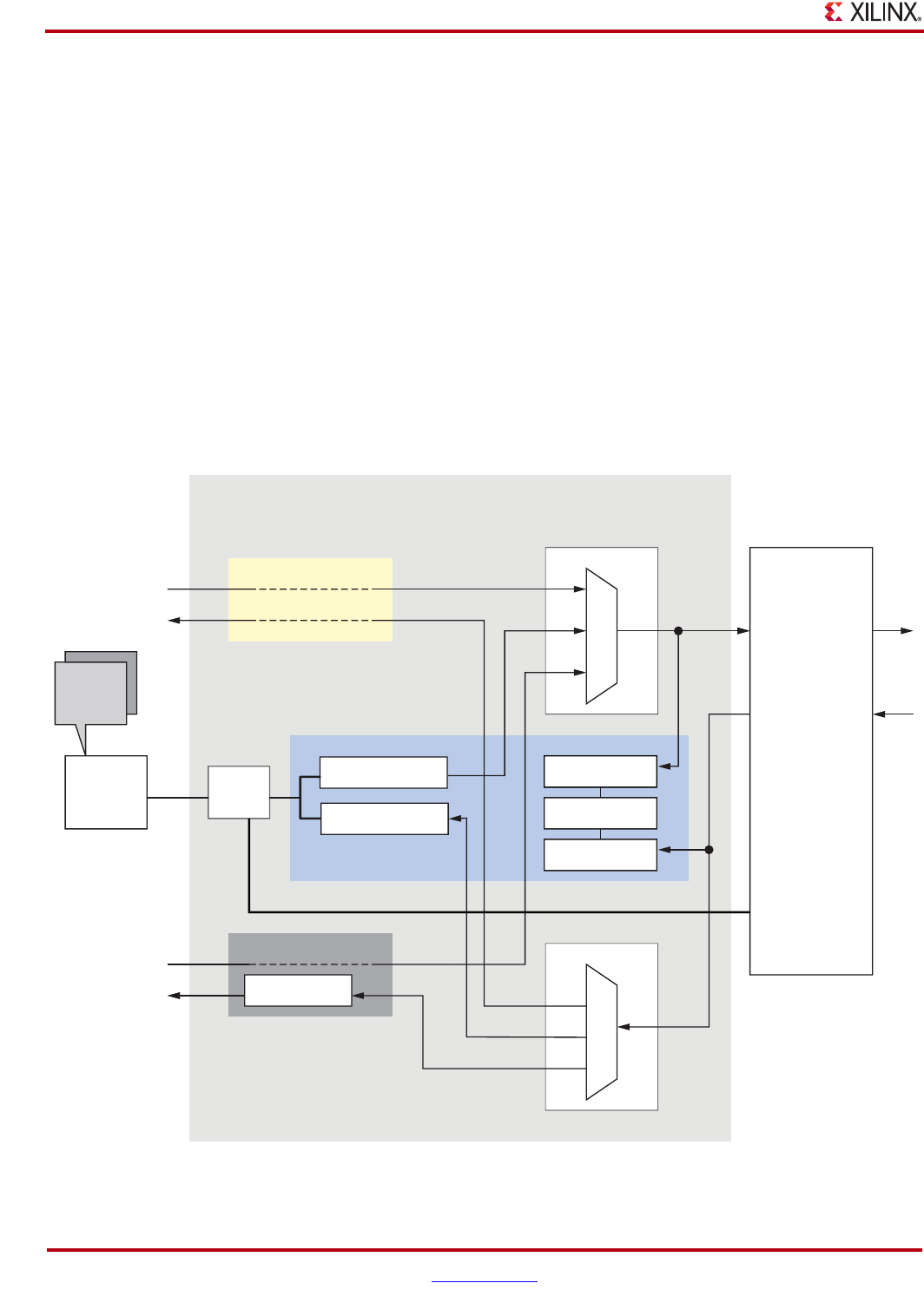

Figure 5-1 illustrates the functional blocks of the Ethernet AVB Endpoint core when it is

generated in standard CORE Generator format. As illustrated, this is intended to be

connected to the LogiCORE IP Tri-Mode Ethernet MAC (or to the LogiCORE IP Embedded

Ethernet Wrappers available in certain Virtex devices).

Each of the functional blocks illustrated will be introduced in the following sections of this

chapter. However, observe from the figure that:

• The Host I/F (management interface) of the Tri-Mode Ethernet MAC is connected

directly to the Ethernet AVB Endpoint LogiCORE IP. This enables the MAC to be fully

configured via the “PLB Interface” of the Ethernet AVB Endpoint core.

• The core provides two independent full-duplex interfaces for customer logic: the “AV

Traffic Interface” and the “Legacy Traffic Interface”.

• The “Legacy Traffic Interface” contains “MAC Header Filters”; these are provided to

replace the Address Filter functionality of the LogiCORE IP Tri-Mode Ethernet MACs

(which must be disabled).

X-Ref Target - Figure 5-1

Figure 5-1: Ethernet AVB Endpoint Core Block Diagram for Connection to LogiCORE IP Tri-Mode Ethernet

MAC

Tx

Rx

PLB

Tx Arbiter

Rx Splitter

PLB I/F

PLB I/F

MAC Header Filters

.c, .h

software

drivers

Ethernet AVB Endpoint

AV

Traffic

Tx

Rx

AV Traffic I/F

Tx Time Stamp

Rx Time Stamp

Real Time Counter

Tx PTP Packet Buffer

Rx PTP Packet Buffer

Precise Timing Protocol (PTP)

Legacy Traffic I/F

Tri-Mode

Ethernet

MAC

Tx Client Tx PHY

Rx PHYRx Client

Embedded

Micro

Processor

Legacy

Traffic

Host I/F