Ethernet AVB Endpoint User Guide www.xilinx.com 127

UG492 July 23, 2010

Using the Xilinx XPS LocalLink Tri-Mode Ethernet MAC

MHS File Syntax

The following code extracts are taken from an XPS project which connected the Ethernet

AVB Endpoint core to an instance of the xps_ll_temac. This design targeted the Virtex-5

family and implemented the xps_ll_temac using an Embedded Tri-Mode Ethernet MAC

macro.

This MHS syntax is included for illustration/guideline purposes. It is recommended that

the XPS GUI is used to import and connect pcore peripherals rather than by manually

editing the .mhs file for a given project. Please refer to Xilinx Platform Studio

documentation.

Certain lines are highlighted and commented to draw attention.

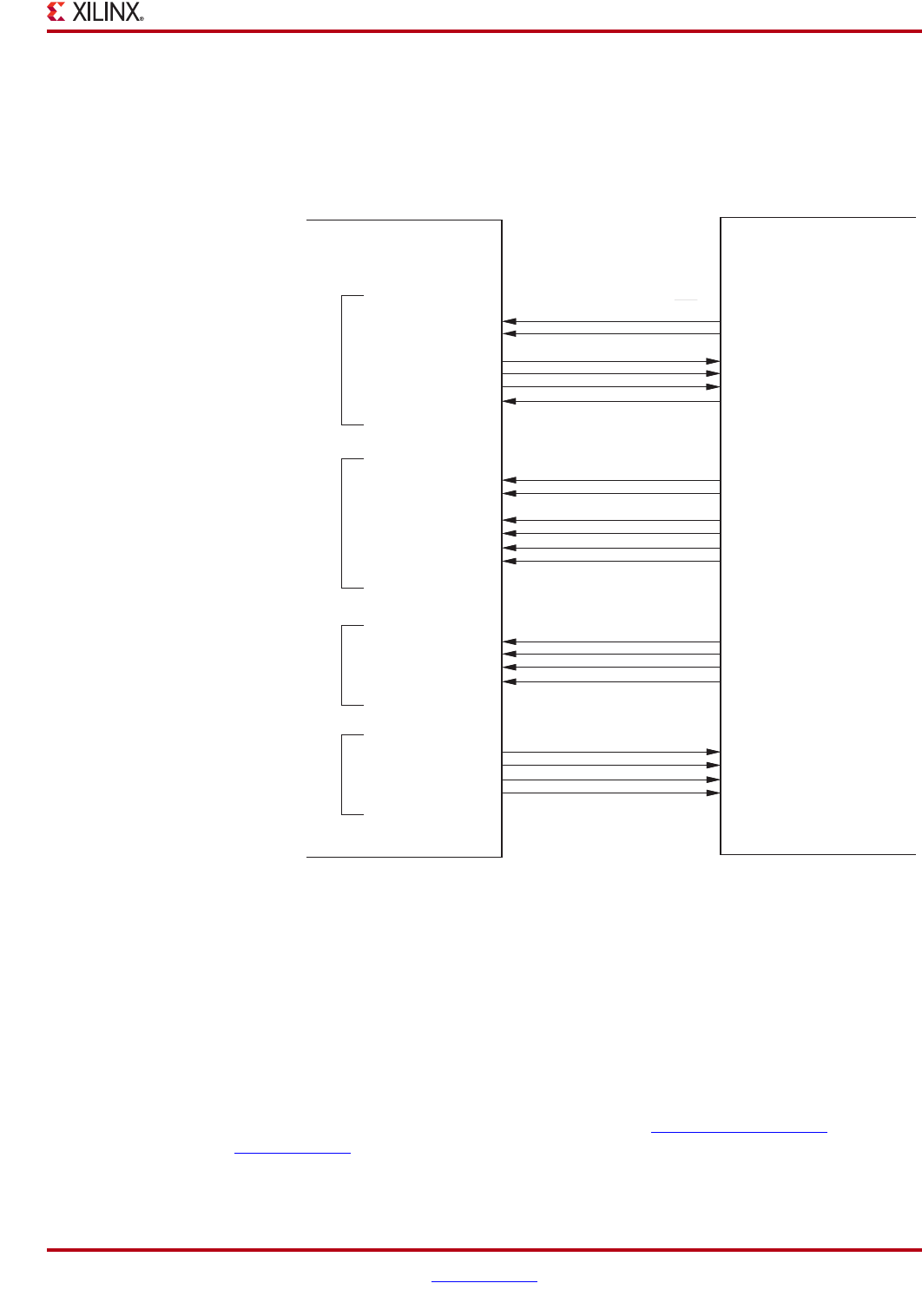

X-Ref Target - Figure 12-9

Figure 12-9: Connection to the XPS LocalLink Tri-Mode Ethernet MAC

tx_clk

tx_clk_enable

tx_data[7:0]

rx_clk

rx_clk_enable

rx_data[7:0]

rx_data_valid

rx_frame_good

rx_frame_bad

Te mac0AvbTxClk

Te mac0AvbTxClkEn

Avb2Mac0TxData[7:0]

Te mac0AvbRxClk

Te mac0AvbRxClkEn

Mac02AvbRxData[7:0]

Mac02AvbRxFrameGood

Mac02AvbRxDataValid

Mac02AvbRxFrameBad

tx_data_valid

tx_underrun

tx_ack

Avb2Mac0TxDataValid

Avb2Mac0TxUnderrun

Mac02AvbTxAck

XPS LocalLink

Tri-Mode Ethernet MAC

(xps_ll_tema

c)

Ethernet AVB Endpoint

pcore

MAC

Transmitter I/F

MAC

Receiver I/F

legacy_tx_data[7:0]

legacy_tx_data_valid

legacy_tx_underrun

legacy_tx_ack

Legacy

Transmitter I/F

legacy_rx_data[7:0]

legacy_rx_data_valid

legacy_rx_frame_good

legacy_rx_frame_bad

Legacy

Recevier I/F

Te mac02AvbTxData[7:0]

Te mac02AvbTxDataValid

Te mac02AvbTxUnderrun

Avb2Temac0TxAck

Avb2Temac0RxData[7:0]

Avb2Temac0RxDataValid

Avb2Temac0RxFrameGood

Avb2Temac0RxFrameBad