Ethernet AVB Endpoint User Guide www.xilinx.com 145

UG492 July 23, 2010

Directory and File Contents

<project directory>/<component name>

The <component name> directory contains the release notes file provided with the core,

which may include last-minute changes and updates.

<component name>/doc

The doc directory contains the PDF documentation provided with the core.

<component name>/example design

The example design directory contains the example design files provided with the core.

For more information, see “Example Design,” page 152.

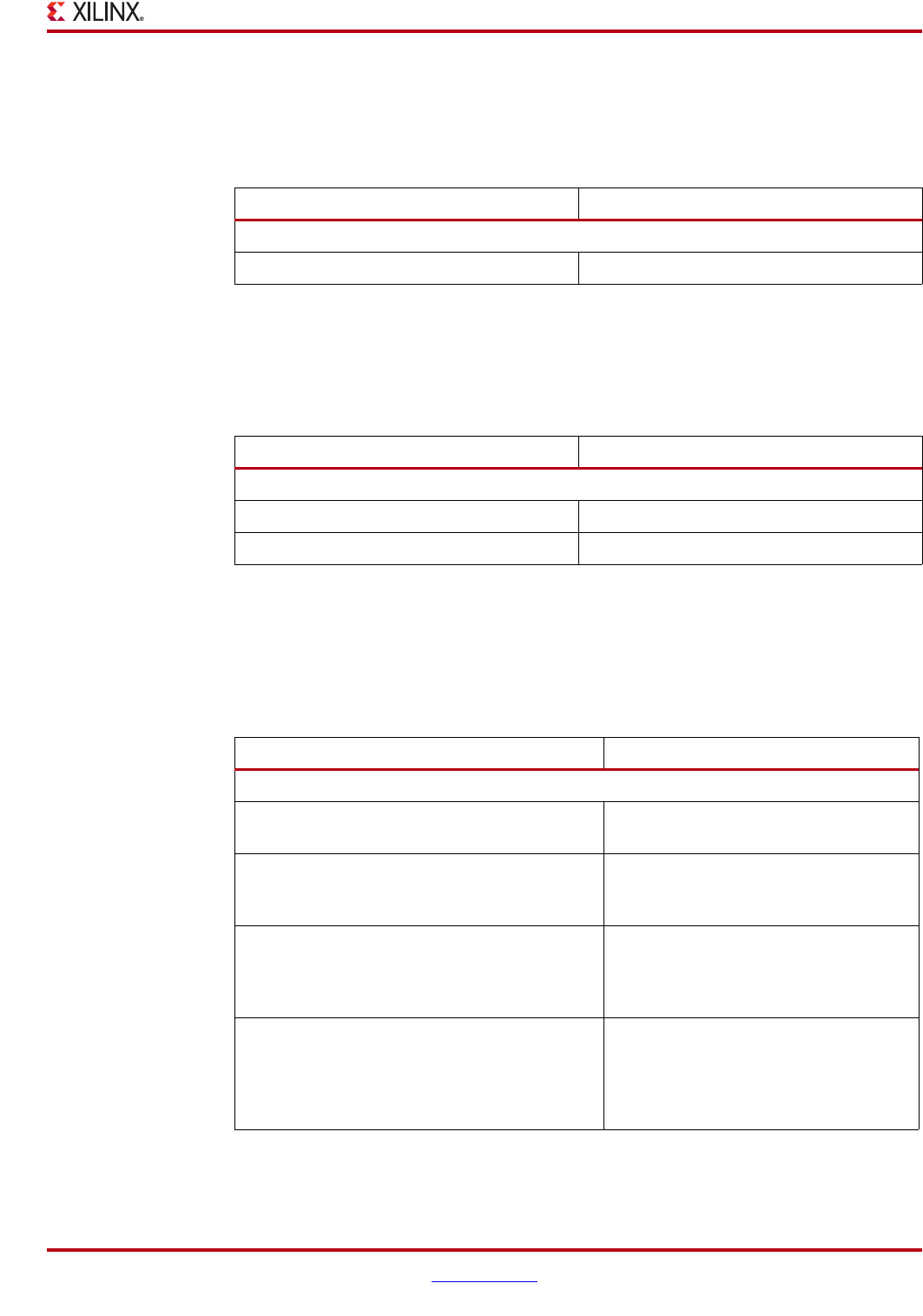

Table 15-2: Component Name Directory

Name Description

<project_dir>/<component_name>

eth_avb_endpoint_readme.txt Core release notes file

Back to Top

Table 15-3: Doc Directory

Name Description

<project_dir>/<component_name>/doc

eth_avb_endpoint_ds677.pdf Ethernet AVB Endpoint Data Sheet

eth_avb_endpoint_ug492.pdf Ethernet AVB Endpoint User Guide

Back to Top

Table 15-4: Example Design Directory

Name Description

<project_dir>/<component_name>/example_design/

<component_name>_example_design.ucf Example User Constraints File (UCF)

provided for the example design.

<component_name>_example_design.v[hd] Top-level file that allows the example

design to be implemented in a device as a

standalone design.

tx_frame_stimulus.v[hd] An HDL file which is capable of

producing Ethernet frames at maximum

line-rate and containing a predictable

pattern in the data field.

temac_loopback_shim.v[hd] An HDL file which sits in the place of an

Ethernet MAC (an Ethernet MAC is

required in a real system). This file loops

back the data from the transmitter client

to the receiver client.