Ethernet AVB Endpoint User Guide www.xilinx.com 121

UG492 July 23, 2010

Using the Xilinx LogiCORE IP Tri-Mode Ethernet MACs

Figure 12-5 can be implemented using the Xilinx tool set using two methods:

• “Using an EDK Project Top Level”

• “Using an ISE Software Top-Level Project”

Using an EDK Project Top Level

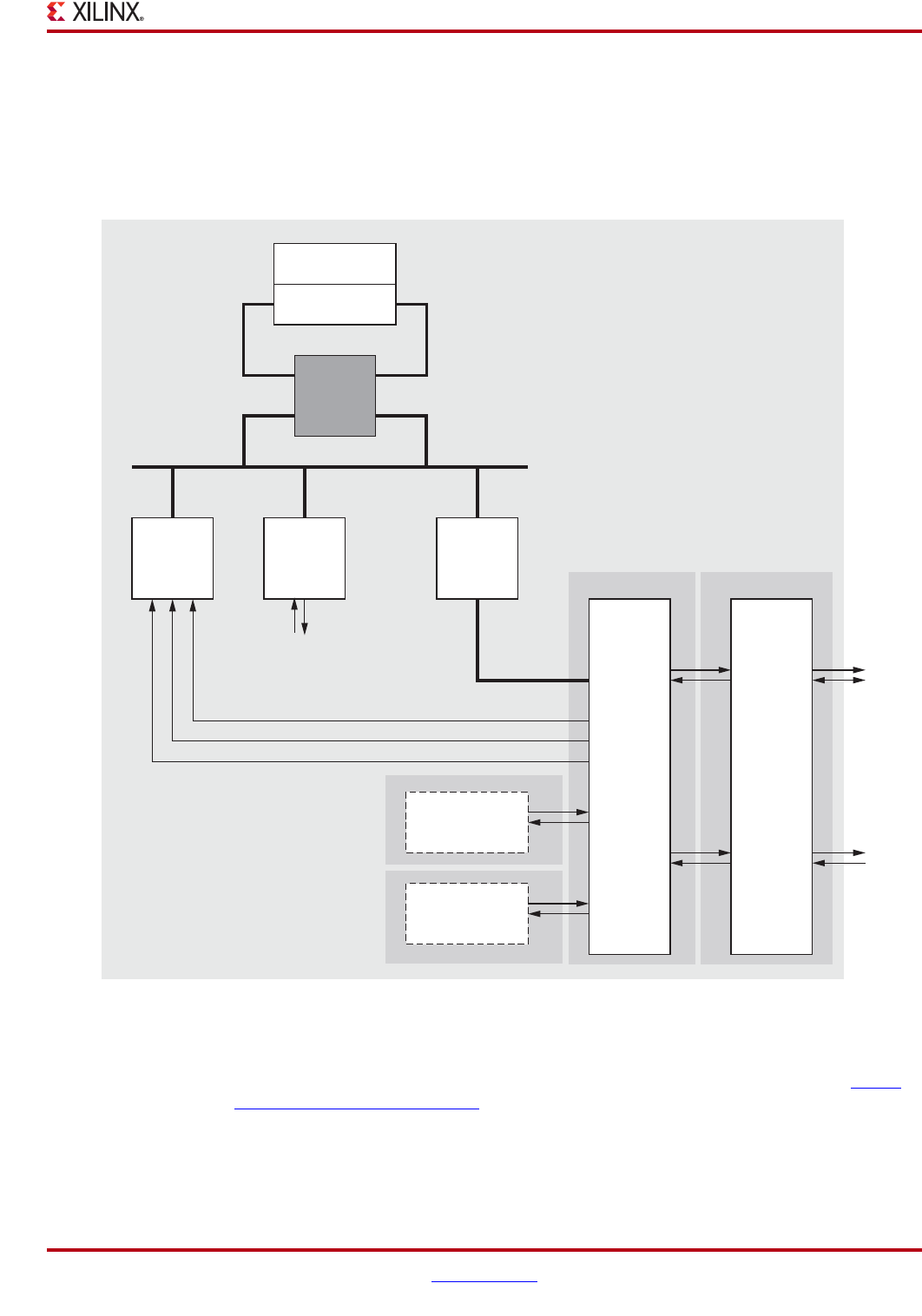

Figure 12-6 shows the implementation using an EDK project. In this hierarchy, the

Ethernet AVB Endpoint, Tri-Mode Ethernet MAC, and all custom logic blocks, must be

manually translated into pcores using the standard pcore approach described in Xilinx

Platform Studio documentation. The standard EDK flow can then be implemented to build

the project.

X-Ref Target - Figure 12-6

Figure 12-6: Connection into an Embedded Processor Sub-system with an EDK Top-level Project

Microblaze

BRAM

xps_intc xps_uartlite

lmb_bram_if_cntlr

Ethernet

AVB

Endpoin

t

TEMAC

Custom AV logic

Custom Legacy logic

PLB

PLB

AV

traffic

I/F

Legacy

traffic

I/F

MAC

client

I/F

Host I/F

interrupt_ptp_timer

interrupt_ptp_rx

interrupt_ptp_tx

pcore:

plb_port

EDK Tool Domain

pcore

pcore

pcore

pcore

MDIO

Ethernet

PHY I/F