Clock Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

6-14 Freescale Semiconductor

6.7.1.8 Oscillator Control Low Register (OCLR)

The OCLR is used to enable and configure the external oscillator.

IPSBAR

Offset: 0x12_000A (OCHR)

Access: Supervisor read/write

76543210

R

OCOEN STBY

— — ————

W

Reset: See note

1

1

The OCOEN reset state is determined during reset configuration.

0000000

Figure 6-8. Oscillator Control High Register (OCHR)

Table 6-12. OCHR Field Descriptions

Field Description

7

OCOEN

On-chip Oscillator Enable bit. This bit enables the relaxation oscillator.

0 Relaxation oscillator is disabled.

1 Relaxation oscillator is enabled.

Note: When switching the clock source to the relaxation oscillator, this bit should be set before

CCLR[OSCSEL] is set.

6

STBY

Relaxation oscillator standby. This bit configures the relaxation oscillator for Standby mode with the output

clock running at 400 kHz.

0 Relaxation oscillator is running in normal mode with an output clock of 8 MHz.

1 Relaxation oscillator is running in standby mode with an output clock of 400 kHz.

5–0 Reserved, should be cleared.

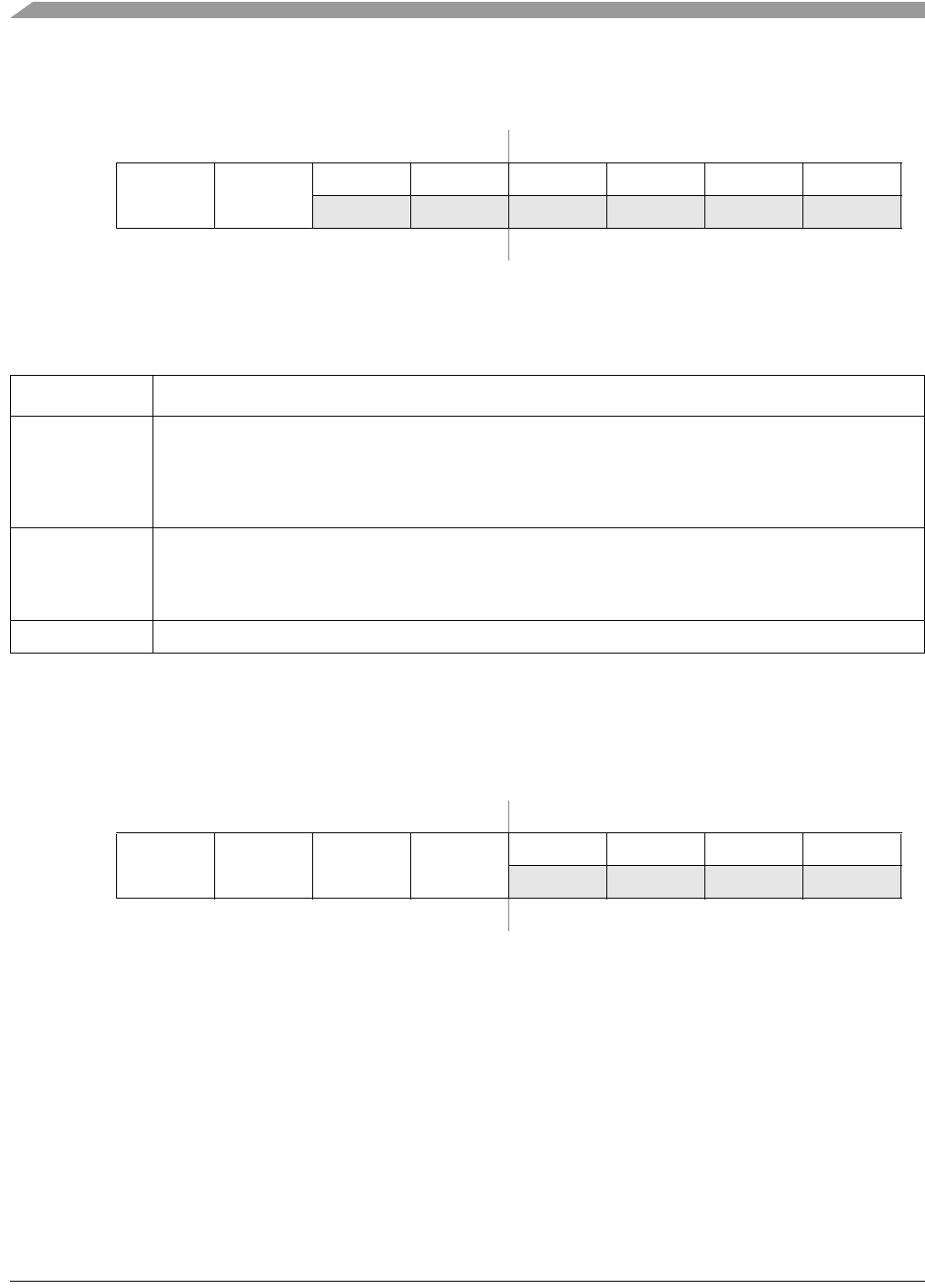

IPSBAR

Offset: 0x12_000B (OCLR)

Access: Supervisor read/write

76543210

R

OSCEN REFS LPEN RANGE

————

W

Reset: See note

1

1

The OSCEN and REFS reset states are determined during reset configuration.

See note 1110000

Figure 6-9. Oscillator Control Low Register (OCLR)