DMA Timers (DTIM0–DTIM3)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

22-6 Freescale Semiconductor

22.2.4 DMA Timer Reference Registers (DTRRn)

Each DTRRn, shown in Figure 22-5, contains the reference value compared with the respective

free-running timer counter (DTCNn) as part of the output-compare function. The reference value is not

matched until DTCNn equals DTRRn, and the prescaler indicates that DTCNn should be incremented

again. Therefore, the reference register is matched after DTRRn + 1 time intervals.

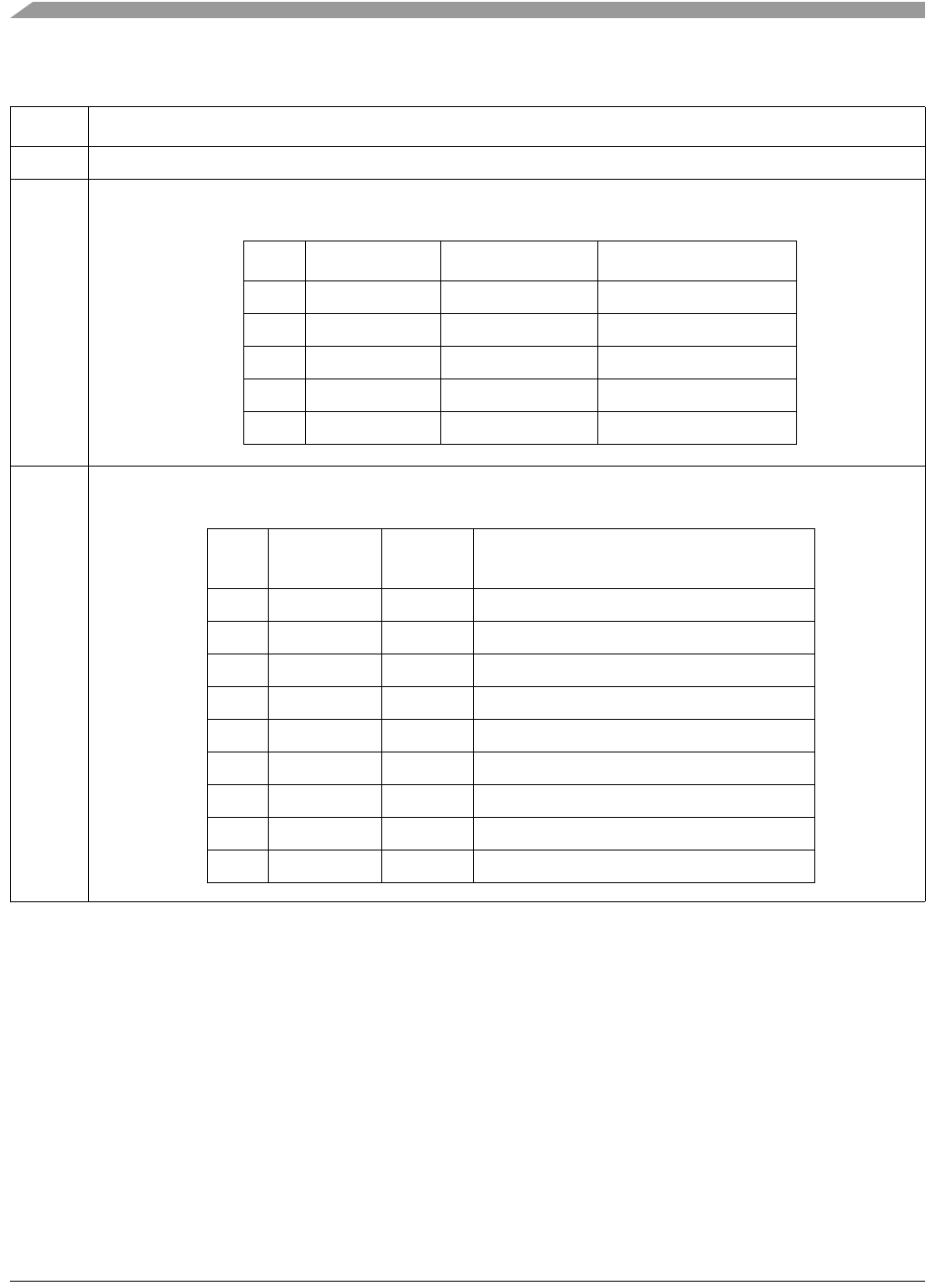

Table 22-4. DTERn Field Descriptions

Field Description

7–2 Reserved, must be cleared.

1

REF

Output reference event. The counter value, DTCNn, equals the reference value, DTRRn. Writing a 1 to REF clears

the event condition. Writing a 0 has no effect.

0

CAP

Capture event. The counter value has been latched into DTCRn. Writing a 1 to CAP clears the event condition.

Writing a 0 has no effect.

REF DTMRn[ORRI] DTXMRn[DMAEN]

0X X No event

1 0 0 No request asserted

1 0 1 No request asserted

1 1 0 Interrupt request asserted

1 1 1 DMA request asserted

CAP DTMRn[CE]

DTXMRn

[DMAEN]

0XX X No event

1 00 0 Disable capture event output

1 00 1 Disable capture event output

1 01 0 Capture on rising edge & trigger interrupt

1 01 1 Capture on rising edge & trigger DMA

1 10 0 Capture on falling edge & trigger interrupt

1 10 1 Capture on falling edge & trigger DMA

1 11 0 Capture on any edge & trigger interrupt

1 11 1 Capture on any edge & trigger DMA