Multiply-Accumulate Unit (MAC)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

4-2 Freescale Semiconductor

cycles than comparable non-MAC architectures. For example, small digital filters can tolerate some

variance in an algorithm’s execution time, but larger, more complicated algorithms such as orthogonal

transforms may have more demanding speed requirements beyond scope of any processor architecture and

may require full DSP implementation.

To balance among speed, size, and functionality, the ColdFire MAC is optimized for a small set of

operations that involve multiplication and cumulative additions. Specifically, the multiplier array is

optimized for single-cycle pipelined operations with a possible accumulation after product generation.

This functionality is common in many signal processing applications. The ColdFire core architecture is

also modified to allow an operand to be fetched in parallel with a multiply, increasing overall performance

for certain DSP operations.

Consider a typical filtering operation where the filter is defined as in Equation 4-1.

Eqn. 4-1

Here, the output y(i) is determined by past output values and past input values. This is the general form of

an infinite impulse response (IIR) filter. A finite impulse response (FIR) filter can be obtained by setting

coefficients a(k) to zero. In either case, the operations involved in computing such a filter are multiplies

and product summing. To show this point, reduce Equation 4-1 to a simple, four-tap FIR filter, shown in

Equation 4-2, in which the accumulated sum is a past data values and coefficients sum.

Eqn. 4-2

4.2 Memory Map/Register Definition

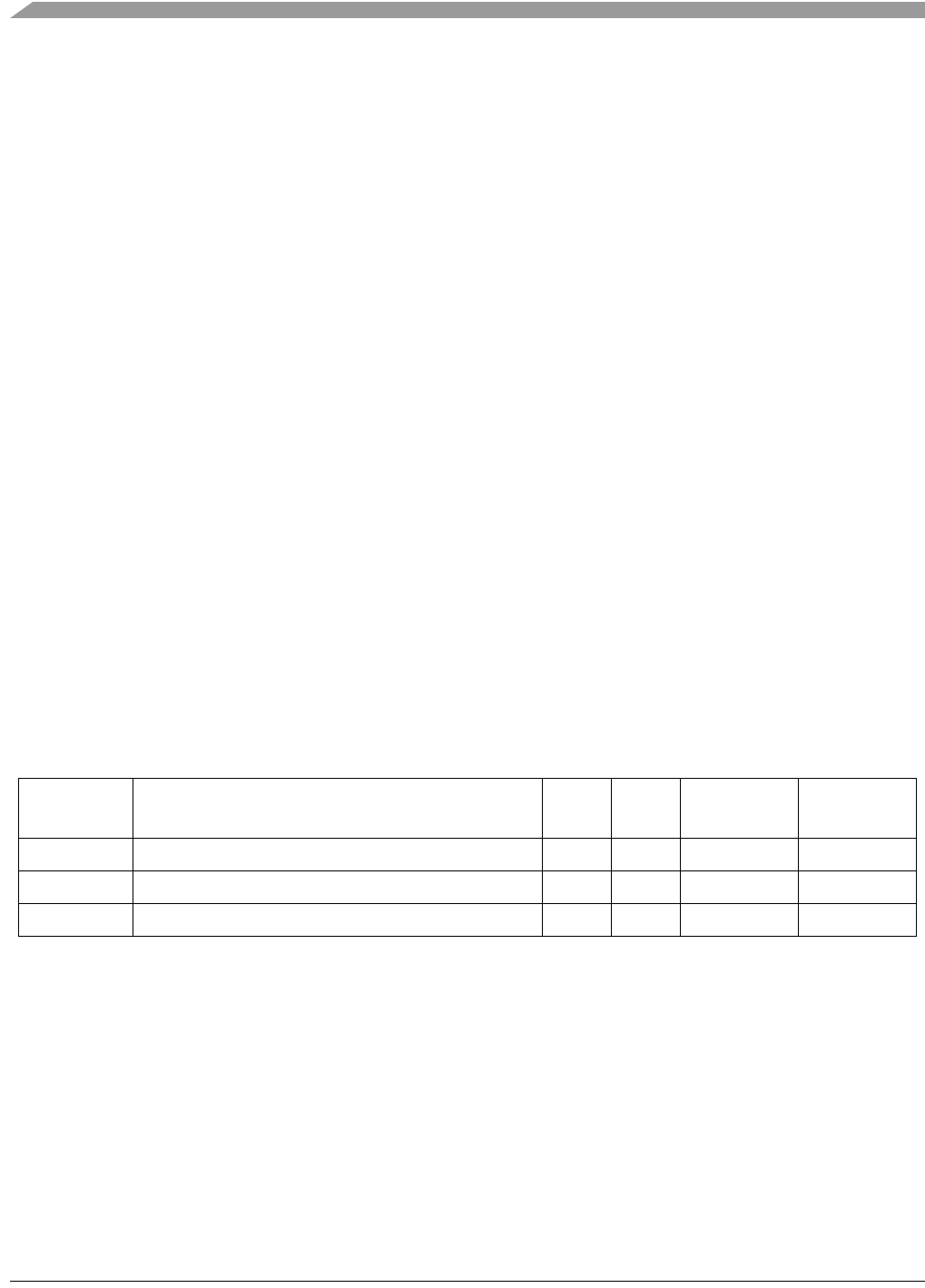

The following table and sections explain the MAC registers:

4.2.1 MAC Status Register (MACSR)

The MAC status register (MACSR) contains a 4-bit operational mode field and condition flags.

Operational mode bits control whether operands are signed or unsigned and whether they are treated as

integers or fractions. These bits also control the overflow/saturation mode and the way in which rounding

is performed. Negative, zero, and overflow condition flags are also provided.

Table 4-1. MAC Memory Map

BDM

1

Register

Width

(bits)

Access Reset Value Section/Page

0x804 MAC Status Register (MACSR) 32 R/W 0x0000_0000 4.2.1/4-2

0x805 MAC Address Mask Register (MASK) 32 R/W 0xFFFF_FFFF 4.2.2/4-4

0x806 Accumulator (ACC) 32 R/W Undefined 4.2.3/4-5

1

The values listed in this column represent the Rc field used when accessing the core registers via the BDM port. For more

information see Chapter 28, “Debug Module.”

yi() ak()yi k–()

k1=

N1–

∑

bk()xi k–()

k0=

N1–

∑

+=

yi() bk()xi k–()

k0=

3

∑

b0()xi() b1()xi 1–()b2()xi 2–()b3()xi 3–()+++==