Debug Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

28-10 Freescale Semiconductor

28.4.3 BDM Address Attribute Register (BAAR)

The BAAR register defines the address space for memory-referencing BDM commands. BAAR[R, SZ]

are loaded directly from the BDM command, while the low-order 5 bits can be programmed from the

external development system. To maintain compatibility with revision A, BAAR is loaded any time the

AATR is written. The BAAR is initialized to a value of 0x05, setting supervisor data as the default address

space.

28.4.4 Address Attribute Trigger Register (AATR)

The AATR defines address attributes and a mask to be matched in the trigger. The register value is

compared with address attribute signals from the processor’s local high-speed bus, as defined by the

4

SSM

Single-Step Mode. Setting SSM puts the processor in single-step mode.

0 Normal mode.

1 Single-step mode. The processor halts after execution of each instruction. While halted, any BDM command

can be executed. On receipt of the

GO command, the processor executes the next instruction and halts again.

This process continues until SSM is cleared.

3–0 Reserved, must be cleared.

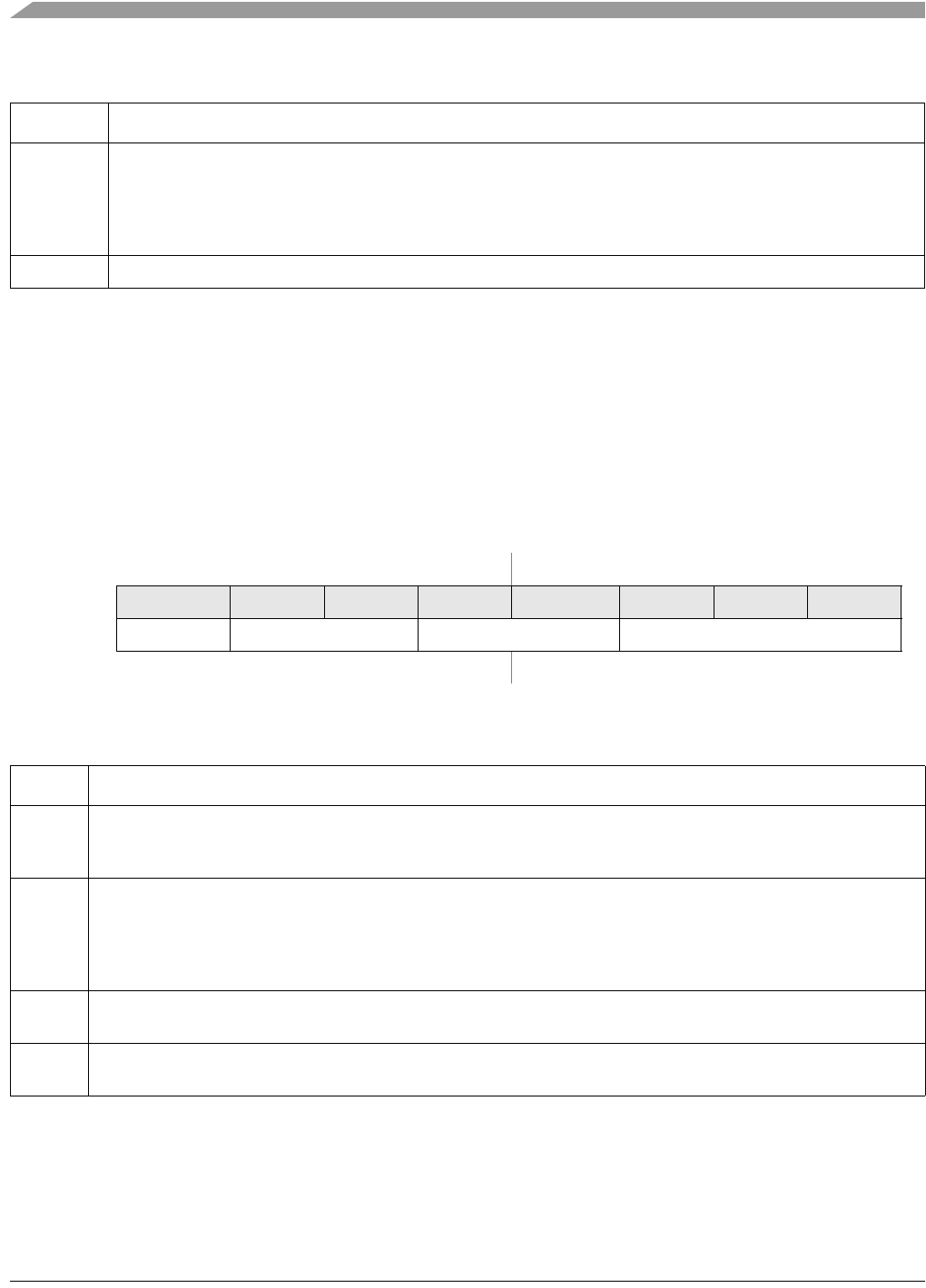

DRc[4:0]: 0x05 (BAAR) Access: Supervisor write-only

BDM write-only

7 6543210

R

W R SZ TT TM

Reset: 0 0 0 0 0 1 0 1

Figure 28-4. BDM Address Attribute Register (BAAR)

Table 28-7. BAAR Field Descriptions

Field Description

7

R

Read/Write.

0Write

1Read

6–5

SZ

Size.

00 Longword

01 Byte

10 Word

11 Reserved

4–3

TT

Transfer Type. See the TT definition in the AATR description, Section 28.4.4, “Address Attribute Trigger Register

(AATR)”.

2–0

TM

Transfer Modifier. See the TM definition in the AATR description, Section 28.4.4, “Address Attribute Trigger Register

(AATR)”.

Table 28-6. CSR Field Descriptions (continued)

Field Description