I

2

C Interface

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

25-10 Freescale Semiconductor

25.3.4 Acknowledge

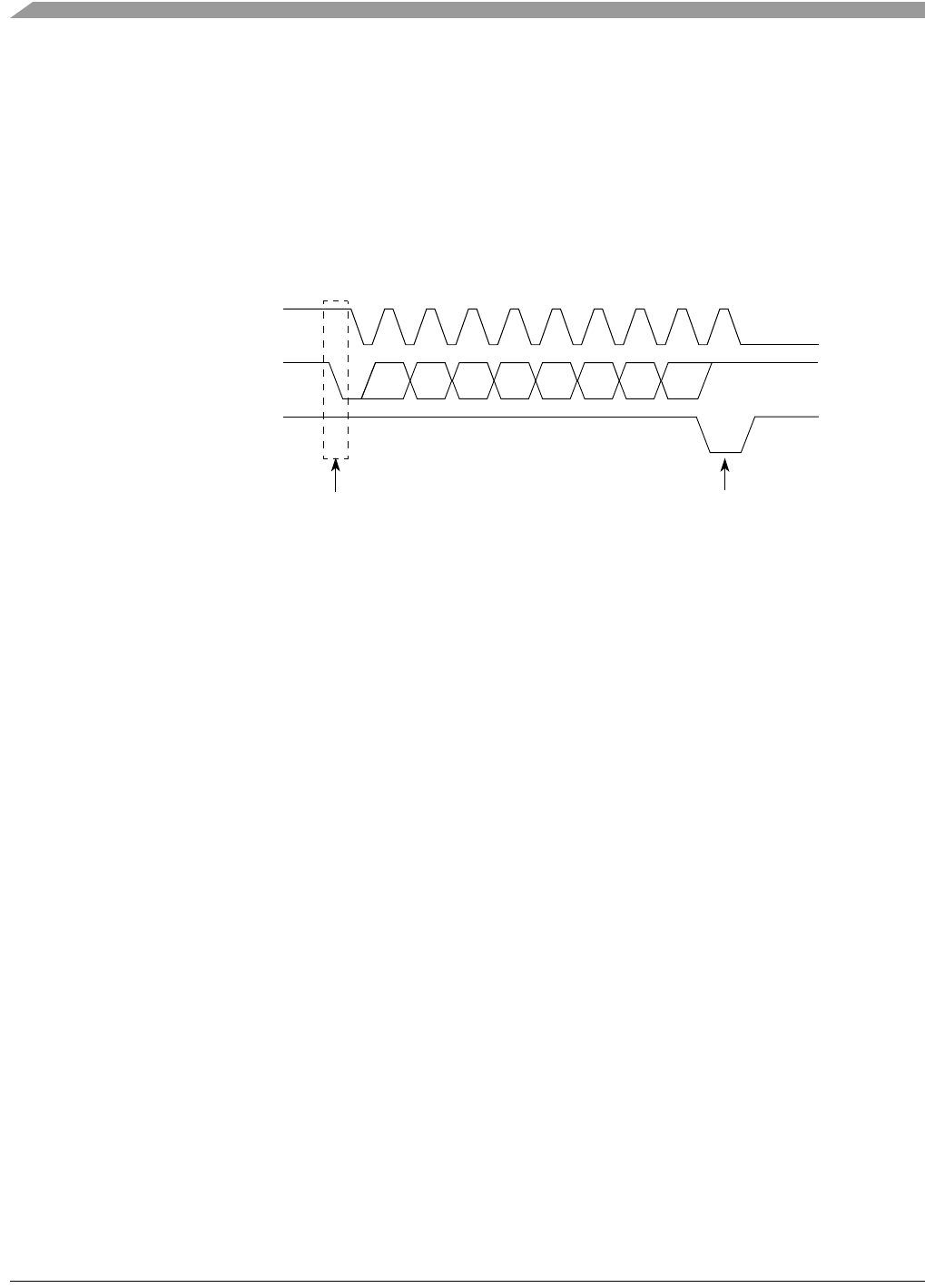

The transmitter releases the SDA line high during the acknowledge clock pulse as shown in Figure 25-9.

The receiver pulls down the SDA line during the acknowledge clock pulse so that it remains stable low

during the high period of the clock pulse.

If it does not acknowledge the master, the slave receiver must leave SDA high. The master can then

generate a STOP signal to abort data transfer or generate a START signal (repeated start, shown in

Figure 25-10 and discussed in Section 25.3.6, “Repeated START”) to start a new calling sequence.

Figure 25-9. Acknowledgement by Receiver

If the master receiver does not acknowledge the slave transmitter after a byte transmission, it means

end-of-data to the slave. The slave releases SDA for the master to generate a STOP or START signal

(Figure 25-9).

25.3.5 STOP Signal

The master can terminate communication by generating a STOP signal to free the bus. A STOP signal is

defined as a low-to-high transition of SDA while SCL is at logical high (see F in Figure 25-7). The master

can generate a STOP even if the slave has generated an acknowledgment, at which point the slave must

release the bus. The master may also generate a START signal following a calling address, without first

generating a STOP signal. Refer to Section 25.3.6, “Repeated START.”

25.3.6 Repeated START

A repeated START signal is a START signal generated without first generating a STOP signal to terminate

the communication, as shown in Figure 25-10. The master uses a repeated START to communicate with

another slave or with the same slave in a different mode (transmit/receive mode) without releasing the bus.

567894321

Bit6 Bit4 Bit3 Bit2 Bit1Bit5Bit7

Bit0

START Signal

R/W

ACK

SCL

SDA by Transmitter

SDA by Receiver