Interrupt Controller Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

14-6 Freescale Semiconductor

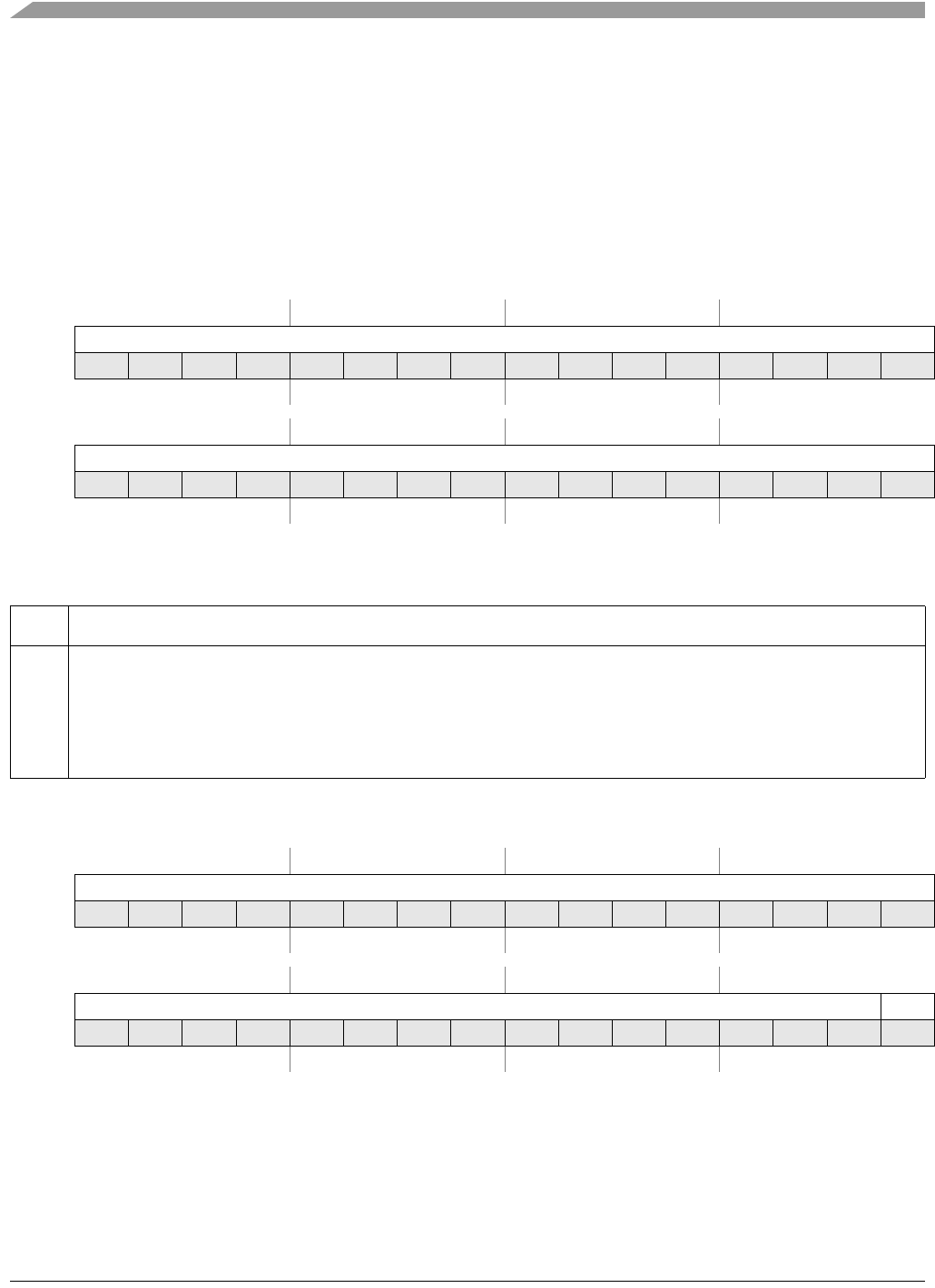

14.3.1 Interrupt Pending Registers (IPRHn, IPRLn)

The IPRHn and IPRLn registers, Figure 14-1 and Figure 14-2, each 32 bits, provide a bit map for each

interrupt request to indicate if there is an active request (1 = active request, 0 = no request) for the given

source. The state of the interrupt mask register does not affect the IPRn. The IPRn is cleared by reset. The

IPRn is a read-only register, so any attempted write to this register is ignored. Bit 0 is not implemented and

reads as a zero.

IPSBAR

Offset: 0x0C00 (IPRHn)

Access: Read-only

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R INT[63:48]

W

Reset0000000000000000

1514131211109876543210

R INT[47:32]

W

Reset0000000000000000

Figure 14-1. Interrupt Pending Register High (IPRHn)

Table 14-3. IPRHn Field Descriptions

Field Description

31–0

INT

Interrupt pending. Each bit corresponds to an interrupt source. The corresponding IMRHn bit determines whether an

interrupt condition can generate an interrupt. At every system clock, the IPRHn samples the signal generated by the

interrupting source. The corresponding IPRHn bit reflects the state of the interrupt signal even if the corresponding

IMRHn bit is set.

0 The corresponding interrupt source does not have an interrupt pending

1 The corresponding interrupt source has an interrupt pending

IPSBAR

Offset: 0x0C04 (IPRLn)

Access: Read-only

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R INT[31:16]

W

Reset0000000000000000

1514131211109876543210

R INT[15:1] 0

W

Reset0000000000000000

Figure 14-2. Interrupt Pending Register Low (IPRLn)