Analog-to-Digital Converter (ADC)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 26-13

26.4.7 Limit Status Register (ADLSTAT)

The ADC limit status (ADLSTAT) register latches in the result of the comparison between the result of the

sample in the ADRSLTn register and the respective limit register, ADHLMTn or ADLLMTn.

For example, if the result for ADRSLT0 is greater than the value programmed into ADHLMT0, then the

the HLS0 bit is set. An interrupt is generated if CTRL1[HLMTIE] is set.

These bits are sticky—they are not cleared automatically by subsequent conversions. A bit may only be

cleared by writing a 1 to it.

8

HLMTI

High Limit Interrupt bit. If any high limit register (ADHLMTn) is enabled by having a value other than 0x7FF8,

high limit checking is enabled. This bit is set at the completion of an individual conversion which may or may

not be the end of a scan. It is cleared by writing 1 to all active ADLSTAT[HLS] bits.

0 No high limit interrupt request

1 High limit exceeded, IRQ pending if CTRL1[HLMTIE] is set

7–0

RDYn

Ready Sample bits. These bits indicate samples 7-0 are ready to be read. The RDYn bits are set as the

individual channel conversions are completed and stored in a ADRSLTn register. These bits are cleared after

a read from the corresponding ADC results (ADRSLTn) register. If polling the RDYn bits to determine if a

particular sample is executed, care should be taken not to start a new scan until all enabled samples are

completed.

0 Sample not ready or has been read

1 Sample ready to be read

Note: RDYn bits can be cleared when the debugger reads the corresponding results register during a debug

session.

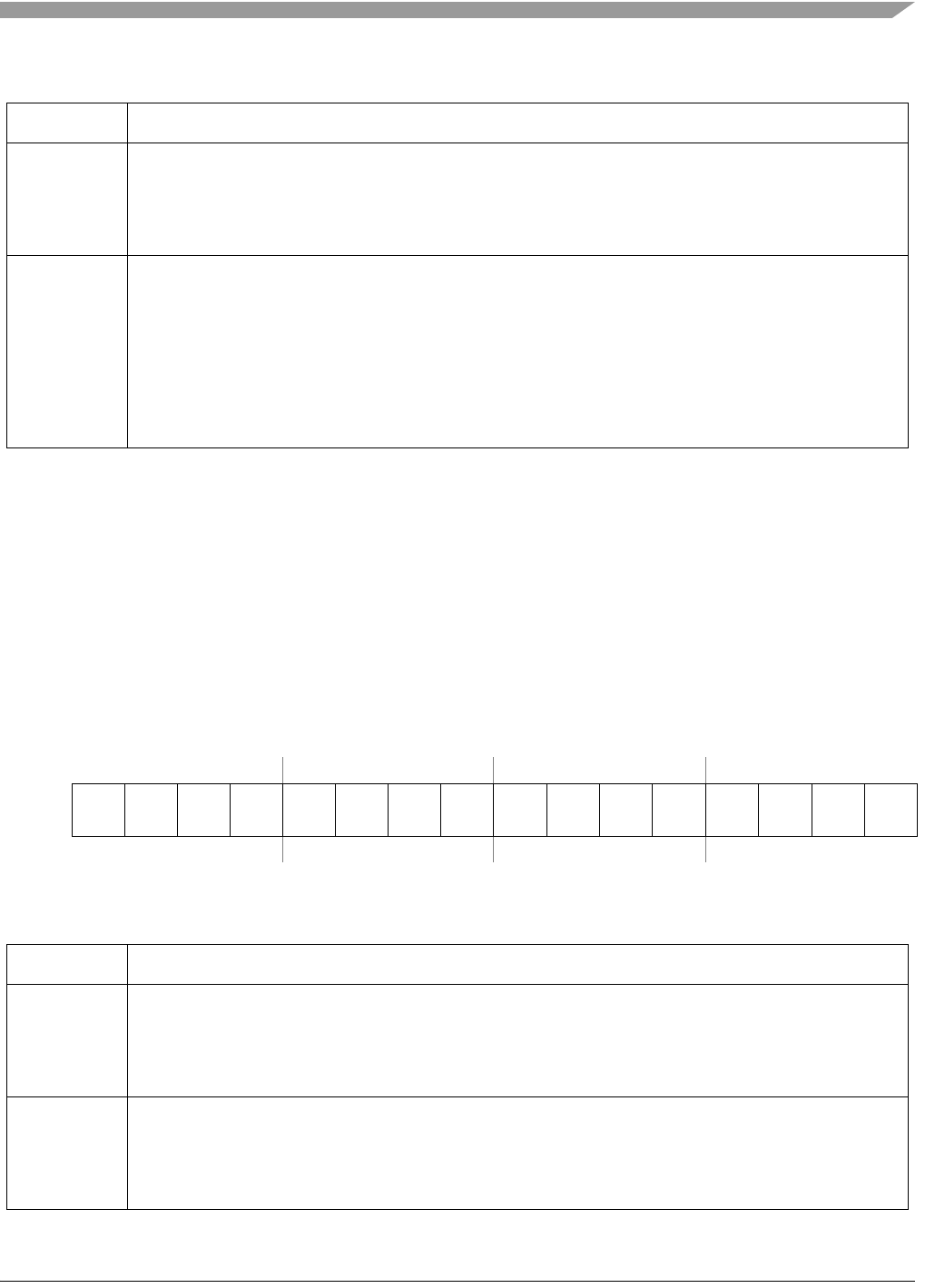

IPSBAR

Offset: 0x19_000E (ADLSTAT)

Access: read/write

1514131211109876543210

R

HLS7 HLS6 HLS5 HLS4 HLS3 HLS2 HLS1 HLS0 LLS7 LLS6 LLS5 LLS4 LLS3 LLS2 LLS1 LLS0

W

Reset0000000000000000

Figure 26-10. Limit Status Register (ADLSTAT)

Table 26-12. ADLSTAT Field Descriptions

Field Description

15–8

HLSn

High Limit Status bits. These bits hold the result of a comparison between the sample (stored in ADRSLTn)

and the high-limit value (stored in ADHLMTn).

0 Sample n is less than or equal to the associated high-limit value

1 Sample n is greater than the associated high-limit value

Note: These bits are sticky, and can only be cleared by writing a 1 to them.

7–0

LLSn

Low Limit Status bits. These bits hold the result of a comparison between the sample (stored in ADRSLTn)

and the low-limit value (stored in ADLLMTn).

0 Sample n is greater than or equal to the associated low-limit value

1 Sample n is less than the associated low-limit value

Note: These bits are sticky, and can only be cleared by writing a 1 to them.

Table 26-11. ADSTAT Field Descriptions (continued)

Field Description