MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor B-1

Appendix B

Revision History

This appendix describes corrections to the MCF52211 Reference Manual. For convenience, the corrections

are grouped by revision.

B.1 Changes between Rev. 1 and Rev. 2

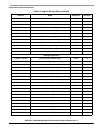

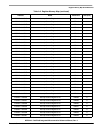

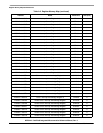

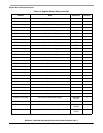

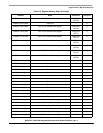

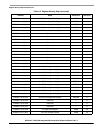

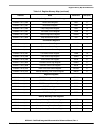

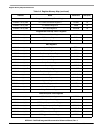

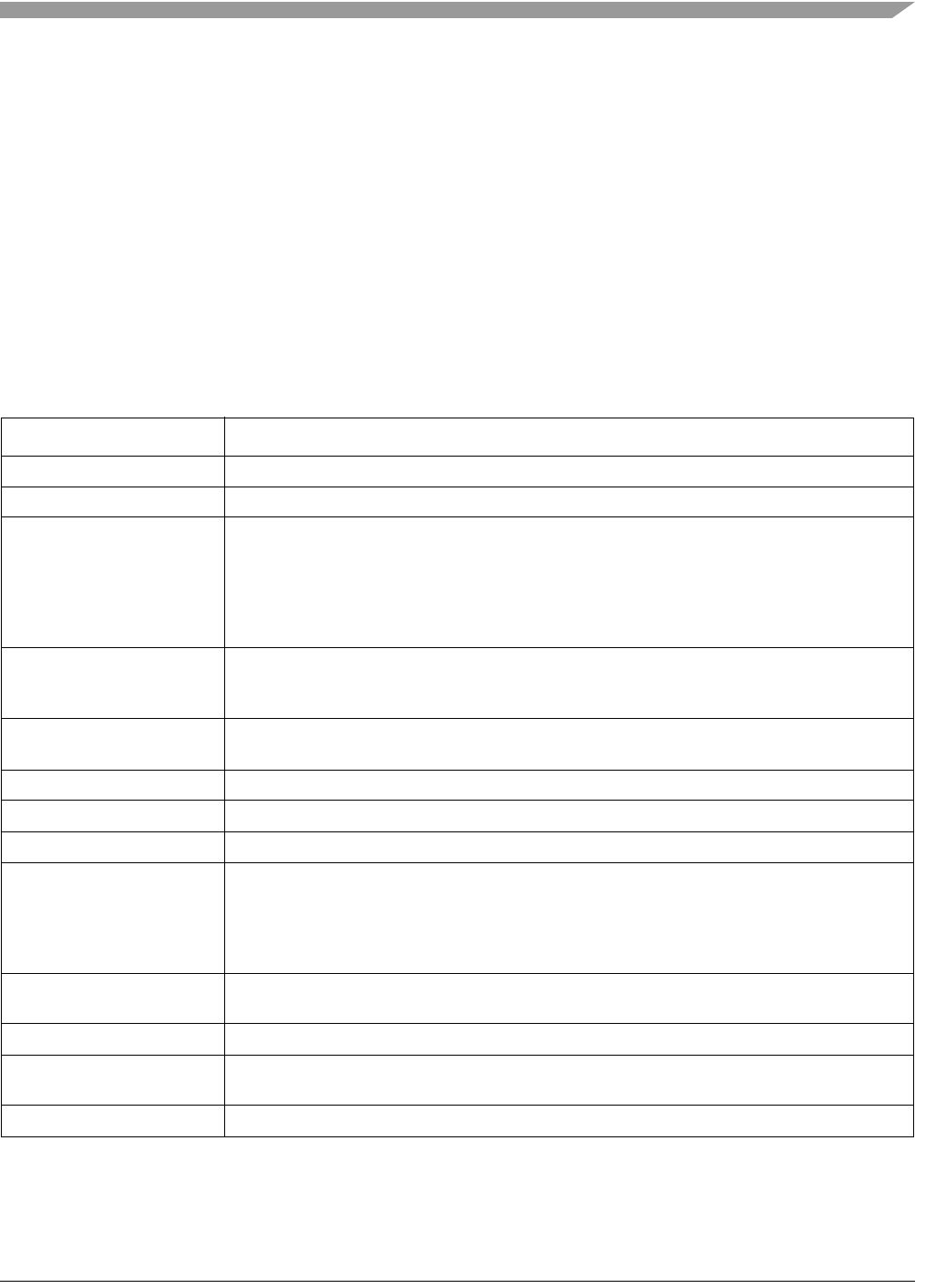

Table 1. MCF52211RM Rev. 1 to Rev. 2 Changes

Location Description

Throughout Formatting, layout, spelling, and grammar corrections.

Chapter 1 Added information about the MCF52212 and MCF52213 devices.

Table 2-1 / Page 2-6 • Changed the GPTn pin assignments for the 64-pin package (were 40...43, are “—” for all

pins).

• Removed the entries for the following signals (not visible off-chip): USB_RPU, USB_ID,

USB_VBUSVLD, USB_PULLUP, USB_SESSEND, USB_SESSVLD, USB_ALT_CLK,

USB_DP_PDOWN, USB_DM_PDOWN, USB_PULLUP, USB_VBUSE, USB_VBUSD,

USB_RCV, USB_SPEED, USB_VBUSCHG, USB_VBUSDIS, USB_DPO, USB_DMO

Figure 6-1 / Page 6-4 • Moved the divide-by-2 block (was downstream of the STOP MODE gate, is downstream of

the PPRML[1] gate).

• Added a note that a 48 MHz frequency is required for the USB module.

Figure 6-4 / Page 6-11 Deleted the sentence “The bits reset to 0b10_0000_0000 during Power-On Reset” from the

footnote.

Figure 6-12 / Page 6-19 Updated the figure with new frequency and capacitance values.

Table 8-1 / Page 8-1 Changed the reset value for PPMRL (was 0x1, is 0x8).

Section 8.2.1.1 / Page 8-4 Corrected the descriptions of bits 3 and 2 to match the register’s correct reset value.

Figure 13-1 / Page 13-1 • Removed the entries for the following signals (not visible off-chip): USB_RPU, USB_ID,

USB_VBUSVLD, USB_PULLUP, USB_SESSEND, USB_SESSVLD, USB_ALT_CLK,

USB_DP_PDOWN, USB_DM_PDOWN, USB_PULLUP, USB_VBUSE, USB_VBUSD,

USB_RCV, USB_SPEED, USB_VBUSCHG, USB_VBUSDIS, USB_DPO, USB_DMO

• Deleted the PWM7 and PWM1 signals from port UA.

Section 18.4.3 / Page 18-31 • Deleted the duplicate “JTAG Lockout Recovery” section.

• Added the “EzPort Lockout Recovery” section.

Table 22-1 / Page 22-3 Corrected DTRRn reset value (was 0x1111_1111, is 0xFFFF_FFFF).

Table 26-19 / Page 26-20 Changed the description for SEL_VREFH=0 and SEL_VREFL=0 (were “Internal VRx”, are

“VRH” and “VRL”, respectively).

Section 28.4 / Page 28-6 Clarified the last sentence of the first paragraph regarding quiscent DSCLK during WDEBUG.