EM78P259N/260N

8-Bit Microprocessor with OTP ROM

26 •

Product Specification (V1.2) 05.18.2007

(This specification is subject to change without further notice)

Bit 6 ~ Bit 4 (HTS2 ~ HTS0): High time scale bits:

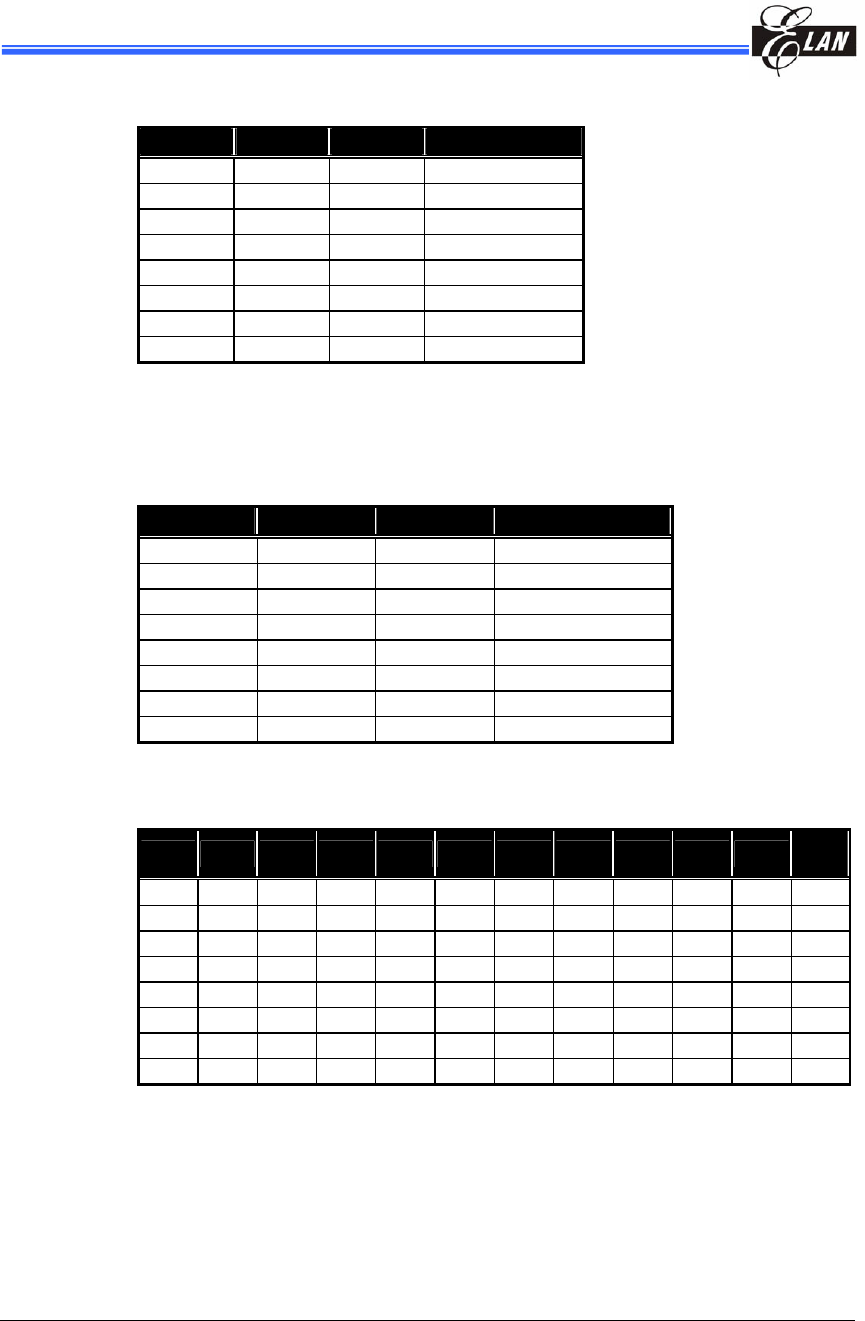

HTS2 HTS1 HTS0 High time Rate

0 0 0 1:2

0 0 1 1:4

0 1 0 1:8

0 1 1 1:16

1 0 0 1:32

1 0 1 1:64

1 1 0 1:128

1 1 1 1:256

Bit 3 (LTSE): Low time scale enable bit.

0 = scale disable bit, Low time rate is 1:1

1 = scale enable bit, Low time rate is set as Bit 2~Bit 0.

Bit 2 ~ Bit 0 (LTS2 ~ LTS0): Low time scale bits:

LTS2 LTS1 LTS0 Low time Rate

0 0 0 1:2

0 0 1 1:4

0 1 0 1:8

0 1 1 1:16

1 0 0 1:32

1 0 1 1:64

1 1 0 1:128

1 1 1 1:256

6.2.19 IOCC1 (TCC Prescaler Counter)

The TCC prescaler counter can be read and written to.

PST2 PST1 PST0 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

TCC

Rate

0 0 0 - - - - - - - V 1:2

0 0 1 - - - - - - V V 1:4

0 1 0 - - - - - V V V 1:8

0 1 1 - - - - V V V V 1:16

1 0 0 - - - V V V V V 1:32

1 0 1 - - V V V V V V 1:64

1 1 0 - V V V V V V V 1:128

1 1 1 V V V V V V V V 1:256

V = valid value

The TCC prescaler counter is assigned to TCC (R1).

The contents of the IOCC1 register are cleared when one of the following occurs:

a value is written to TCC register

a value is written to TCC prescaler bits (Bits 3, 2, 1, 0 of CONT)

power-on reset, /RESET

WDT time-out reset