EM78P259N/260N

8-Bit Microprocessor with OTP ROM

56 •

Product Specification (V1.2) 05.18.2007

(This specification is subject to change without further notice)

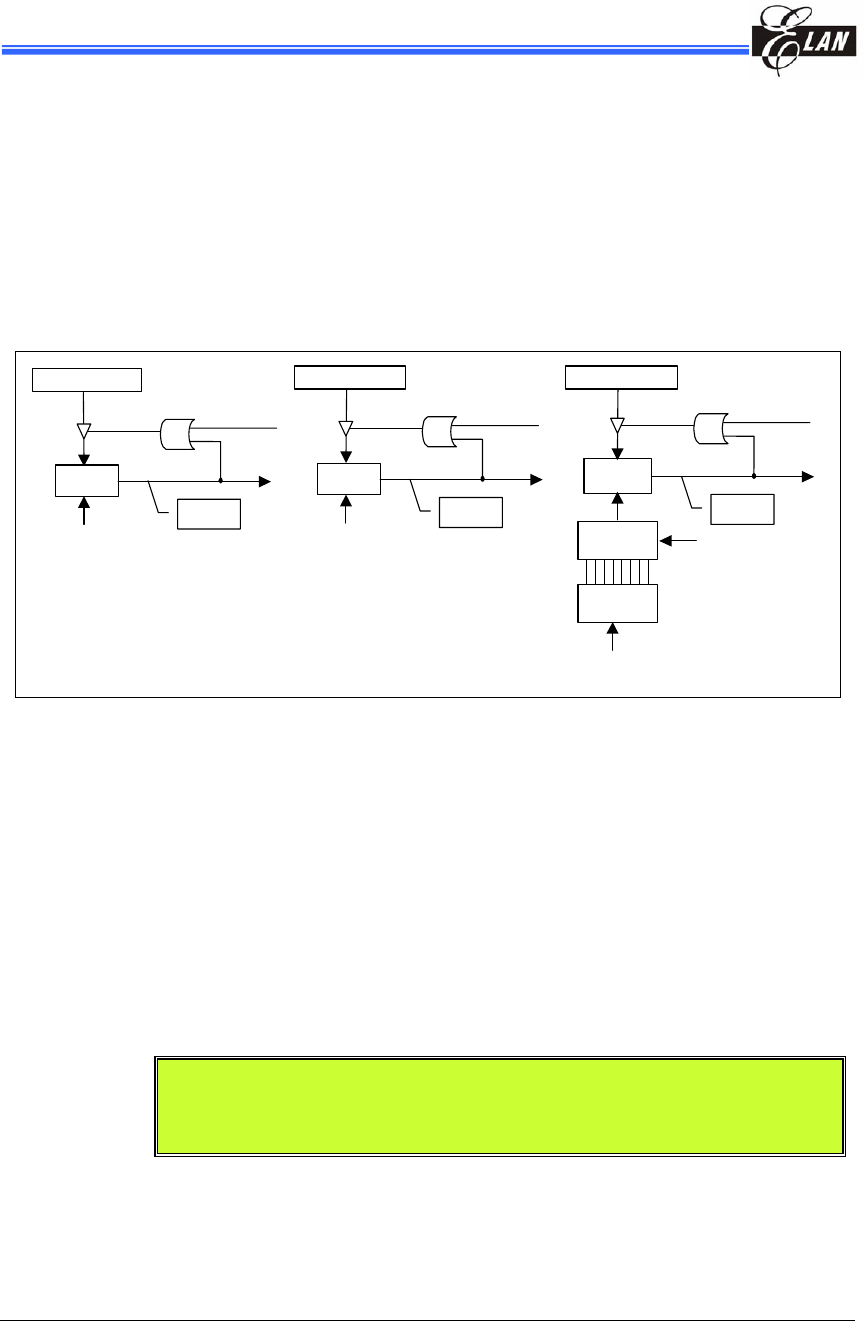

6.9 Timer/Counter

6.9.1 Overview

Timer A (TCCA) is an 8-bit clock counter. Timer B (TCCB) is a 16-bit clock counter.

Timer C (TCCC) is an 8-bit clock counter that can be extended to 16-bit clock counter

with programmable scalers. TCCA, TCCB, and TCCC can be read and written to, and

are cleared at every reset condition.

6.9.2 Function Description

Set predict value

System clock or

External input

External input

TCCC

Set TCCCIF

TCCCEN

Overflow

TCCA

Set TCCAIF

TCCAEN

Overflow

TCCB

Set TCCBIF

TCCBEN

Overflow

Set predict value Set predict value

External input

8-to-1 MUX

8 Bit

counter

System clock or

System clock or

TCCCS1 ~ TCCCS0

Fig. 6-13 Timer Block Diagram

Each signal and block of the above TIMER block diagram is described as follows:

TCCX: Timer A~C register. TCCX increases until it matches with zero, and then

reloads the predicted value. When writing a value to TCCX, the predicted

value and TCCX value become the set value. When reading from TCCX, the

value will be the TCCX direct value. When TCCXEN is enabled, the reload of

the predicted value to TCCX, TCCXIE is also enabled. TCCXIF will be set at

the same time. It is an Up Counter.

Under TCCA Counter (IOC51):

IOC51 (TCCA) is an 8-bit clock counter. It can be read, written to, and cleared

on any reset condition and is an Up Counter.

NOTE

■ TCCA time-out period [1/Fosc x (256-TCCA cnt) x 1 (CLK=2)]

■ TCCA time-out period [1/Fosc x (256-TCCA cnt) x 2 (CLK=4)]

Under TCCB Counter (IOC61):

TCCB (IOC61) is an 8-bit clock counter for the least significant byte of TCCBX

(TCCB). It can be read, written to, and cleared on any reset condition and is an

Up Counter.