Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual 101

Host Software Interface

Link Address

The link address is a 32-bit offset to the next RFD. It is added to the RU base. The link

address of the last frame can be used to form a cyclical link to the first RFD.

Size

This field is used in the simplified mode and represents the data buffer size. In the

header RFD, the size field identifies the data buffer size excluding the header area. The

size value should be an even number.

EOF

This bit is set by the device when it has completed placing data in the data area. Before a

new RFD can be included in the RFA, the EOF bit must be cleared by software.

F

This bit is set by the device when it updates the actual count field. Before a new RFD can

be included in the RFA, the F bit must be cleared by software.

Actual Count The number of bytes written into the data area.

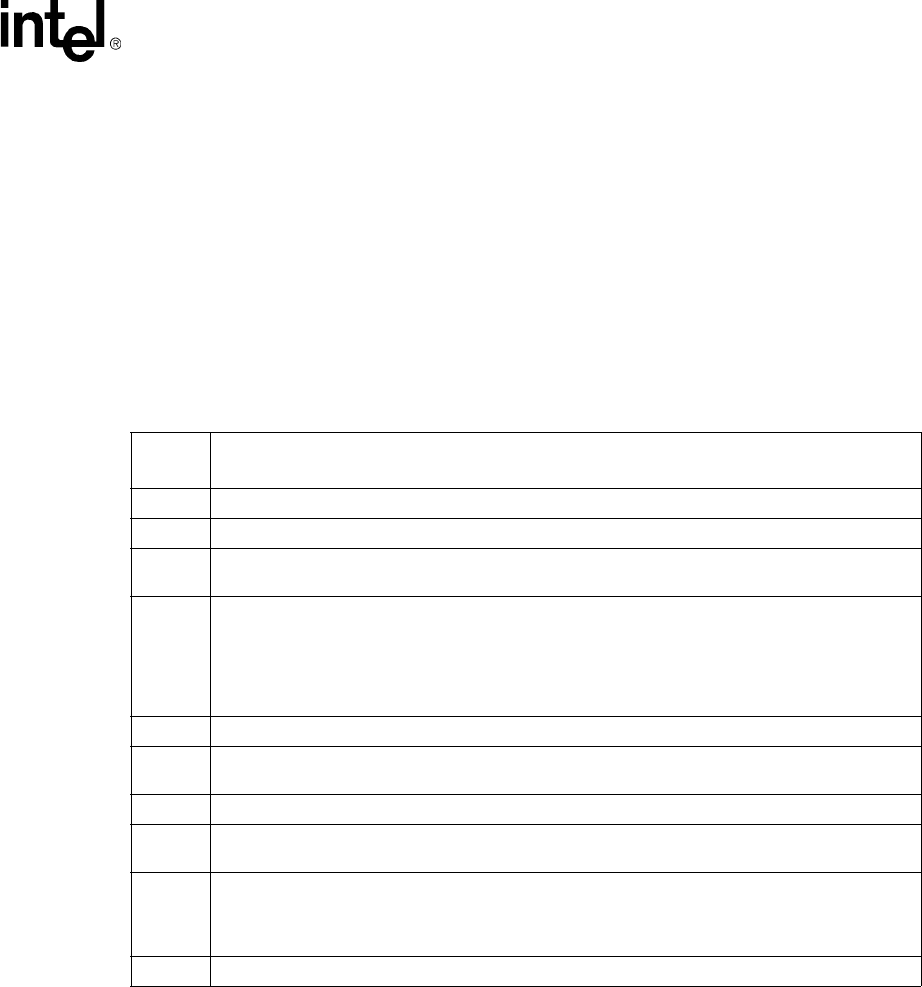

Table 52. RFD Status Bit Descriptions

Status

Bit

Description

Bit 12 This bit is reserved.

Bit 11 CRC error in an aligned frame. This bit may be set only in the save bad frames mode.

Bit 10

Alignment error (CRC error in misaligned frame). This bit identifies the number of bits in the frame

that were not an octet multiple. This bit may be set only in save bad frames mode.

Bit 9

Ran out of buffer space; no resources. This bit indicates that the incoming frame was larger than

the possible receive data area for that frame. In simplified mode, this means that the size of the

RFD was not large enough to accommodate the entire frame.

NOTE: This status bit is not related to the RFD EL and S bits. Status bit 9 reflects the status of the

current frame. The EL and S bits control the RU machine status after the reception of the

current frame.

Bit 8 DMA overrun failure to acquire the system bus. This bit may be set only in save bad frames mode.

Bit 7

Frame too short. It implies that the length of the received frame was less than 64 bytes including

the CRC. This bit may be set only in save bad frames mode.

Bit 6 This bit is reserved.

Bit 5

Type/Length. If this bit is set, it indicates that the received frame was a type frame (the value of the

Ethernet header Type/Length field was either 0 or greater than 1500 decimal).

Bit 4

Receive Error. This bit is set if the RX_ER pin was asserted at least once during frame reception. It

is set by the PHY when it detects a character error. The actual detection of character error depends

on the PHY technology and the algorithm implemented. The device increments the device CRC

error counter when this bit is set. This bit may be set only in save bad frames mode.

Bit 3 This bit is reserved.