Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual 31

Host Software Interface

As the table above indicates, the 8255x have the same alignment restrictions with one exception:

The 82558, and 82559 have a limited capability to support odd byte aligned buffers.

6.3 Controlling the Device

Software issues control commands to the CU and RU through the SCB, which is part of the CSR.

The CPU instructs the device to activate, suspend, resume or idle the CU or RU by placing the

appropriate control command in the CU or RU control field. A CPU write access to the SCB causes

the device to read the SCB, including the Status word, Command word, CU and RU Control fields,

and the SCB General Pointer. Activating the CU causes the device to start executing the CBL.

When execution is completed the device updates the SCB with the CU status then interrupts the

CPU if it is configured. Activating the RU causes the device to access the RFA and go into the

ready state for frame reception. When a frame is received the RU updates the SCB with the RU

status and interrupts the CPU. It also automatically advances to the next free RFD in the RFA. This

interaction between the CPU and the device can continue until a software or selective reset is

issued to the device, at which point the initialization process must be executed again. The CPU can

also perform certain controller functions directly through a CPU port interface.

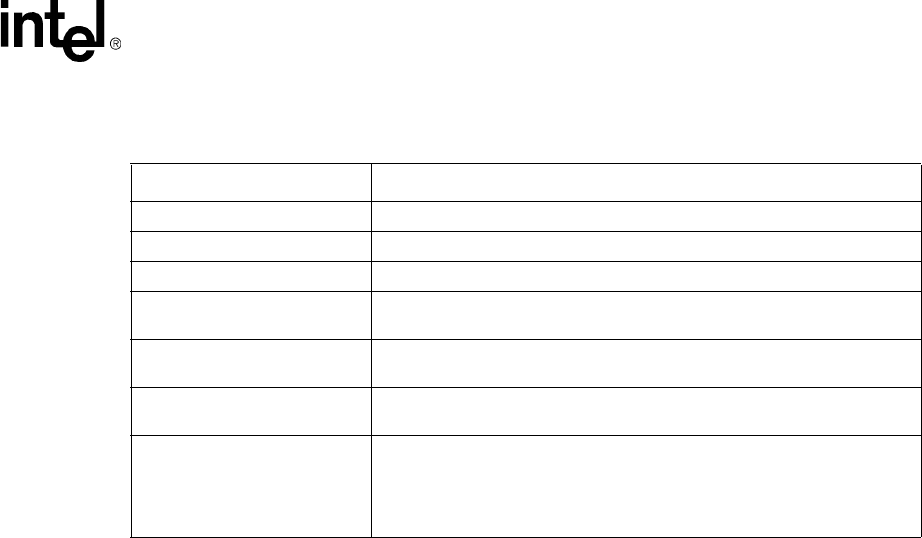

6.3.1 Control / Status Registers (CSR)

The Control/Status Registers make up the CSR space. The basic registers are the SCB Command

word, SCB Status word, SCB General Pointer, Port interface, EEPROM Control register, and MDI

Control register. Additionally, the 82558 and later devices also contain registers for flow control,

power management, etc. All of these registers are shown in the table below. Registers new to the

82558 are lightly shaded, and registers new to the 82559 (at offset 1Ch and beyond) are darkly

shaded. Accessing these higher offset areas in older devices has an unpredictable effect and may

cause errors.

Table 10. Alignment Requirements for 8255x Data Structures

Data Structure Alignment Requirements

Port Self-Test Paragraph aligned (16-byte)

Port Dump Paragraph aligned (16-byte)

CSR and SCB Address allocated by the BIOS. No other alignment requirements.

TxCB (buffer of TxCB in

simplified mode)

Word (even address) aligned (2-byte aligned). However, Dword (4-byte

aligned) structures are more efficient.

TBD

Word (even address) aligned (2-byte aligned). However, Dword (4-byte

aligned) structures are more efficient.

Transmit Buffer (flexible mode

only)

Byte aligned (address can be odd or even).

RFD (buffer of RFD in

simplified mode)

Word (even address) aligned (2-byte aligned). However, Dword (4-byte

aligned) structures are more efficient.

NOTE: In an MWI aware system, for best performance RFDs should be

allocated so that the RFD data area (if not zero) is cache line

aligned.