34 Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

Host Software Interface

— A flow control pause frame was received (FCP Interrupt). This does not apply to the

82557.

Note: TNO interrupts should be avoided. Protocol stacks automatically retry failed transmits. This

feature should only be enabled if software needs to know immediately about transmit failures.

Interrupt events can only be cleared by CPU acknowledgment. In other words, if the device has

asserted its interrupt pin, the only way to clear it is with a CPU Acknowledgment of that particular

interrupt bit in the SCB. Since multiple events could be active simultaneously, if some events are

not acknowledged by the ACK field, the interrupt signal will remain asserted. However, if a new

event occurs while an interrupt is set, it will not cause an additional interrupt.

The table below shows the SCB format. It is followed by a detailed description on the SCB bits and

their functions.

6.3.2.1 SCB Status Word

The SCB Status word is addressable as two bytes. The upper byte is called the STAT/ACK byte,

and the lower, the SCB Status byte. The SCB Status byte indicates the status of the CU and RU.

The STAT/ACK byte reports the device status as bits, which represent the causes of interrupts.

Writing to the STAT/ACK bits will acknowledge pending interrupts. As described below, there are

many different possible interrupt events. The LAN controller asserts the interrupt line to the CPU if

any of these interrupt events need to be serviced. More than one STAT/ACK bits may be set at the

same time. Writing 1 back to a STAT/ACK bit that was set will acknowledge that particular

interrupt bit. The device will de-assert its interrupt line only when all pending interrupt STAT bits

are acknowledged. All pending STAT bits do not need to be acknowledged in a single access, but it

is recommended if the interrupt service routine is likely to process all pending interrupts.

Note: The LAN controller latches interrupts internally. Interrupts are PCI compliant and level-triggered.

Setting a 1 in the interrupt acknowledge command for a non-pending interrupt does not cause any

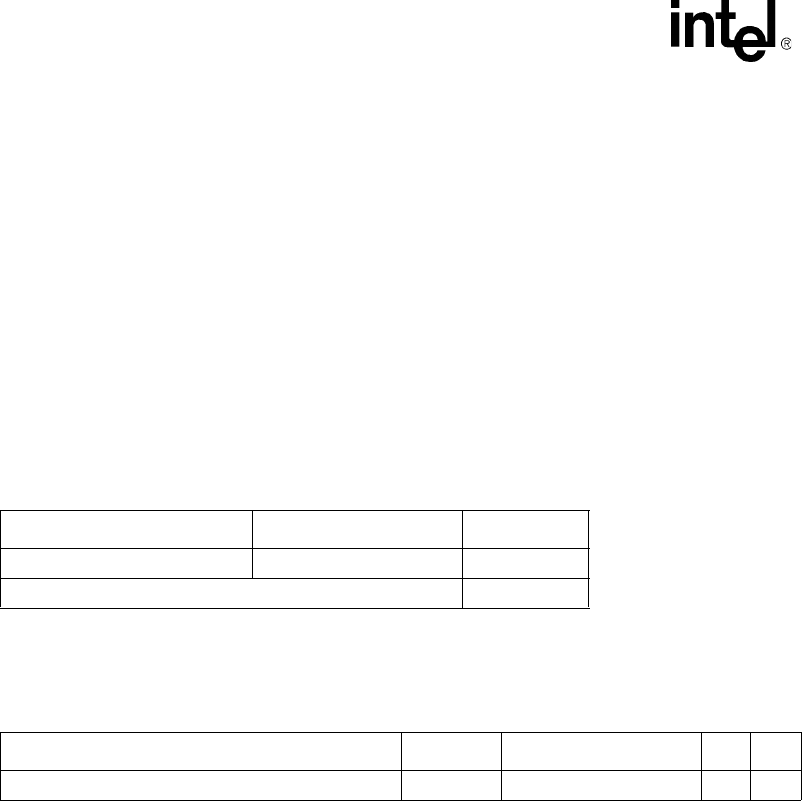

Table 12. System Control Block

31 16 15 0

Upper Word Lower Word Offset

SCB Command Word SCB Status Word Base + 00h

SCB General Pointer Base + 04h

Figure 9. SCB Status Word

15 87 65 2 1 0

STAT / ACK CUS RUS 0 0