10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual 141

Wake-up Functionality

A.3.1 Auxiliary Power Support

The LISTAT signal should be 0 after a hardware reset. For WOL mode, the default value after

power up reset (ALTRST# is asserted) of the PME enable and status bits are:

PME_Enable = 1 (wake up is enabled)

PME_status = 0 (no wake-up event)

Since the OS/BIOS expect unknown values in these bits after power up, they will clear both bits

using PCI configuration command. If WOL mode is enabled, the device will wake up the system

when it receives a Magic Packet* after power up without any need for software interaction.

A.3.2 Auxiliary Power Non-support

If the system does not support and auxiliary power source, LISTAT is floating after a hardware

reset. In this case wake up from D3

cold

is not supported. Both the PME enable and status bits

should equal 0 after any hardware reset. To enable the WOL functionality, the PME enable bit is

bypassed if WOL mode is enabled and auxiliary power indication is not active (same as 82558A).

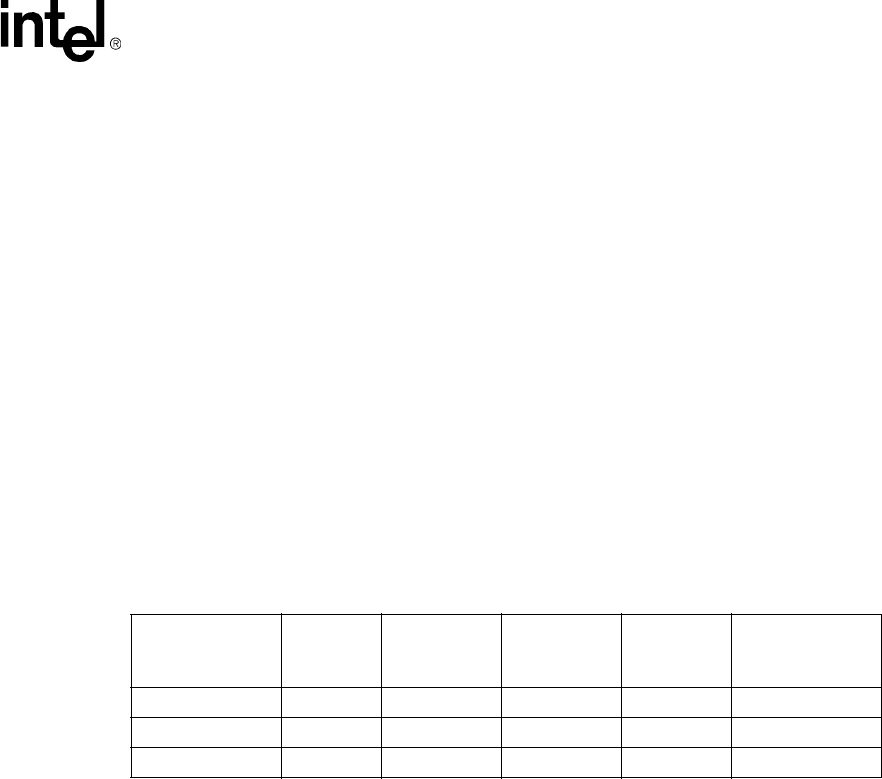

The table below summarizes the PME enable and status bits default values and properties in

different configurations.

NOTE: When the WOL bit in the EEPROM is set and auxiliary power is not supported, the PME enable bit is

always ignored regardless of the wake-up event type.

A.4 Fixed Packet Filtering

Fixed packet filtering includes the wake up capabilities implemented in the hardware with a pre-

defined fixed pattern. It includes Address Match packets, Magic Packets, and ARP packets. The

device filters all incoming frames, monitoring for one of the packet types mentioned, regardless of

the power state. Each fixed filter can be enabled using the configuration command. When the

corresponding filter bit is enabled, the device asserts PME# for frames passing the filter with a

correct CRC value. This filtering mechanism is active when power is supplied to the device with or

without an active clock on the PCI bus.

Any packet that passes address filtering is transferred to the internal micromachine. The

micromachine may store or further analyze the packet if the following conditions are met:

• Loadable microcode for analyzing and storing the packet in the micromachine resources is

active.

• The clock signal is active on the PCI CLK pin. This may be the PCI bus clock or any other

clock generated by an external clock switching circuitry.

Auxiliary Power

(indicated by

LISTAT)

WOL bit

(EEPROM)

PME Enable

Default

(ALTRST#)

PME Status

Default

(ALTRST#)

RST# clears

bits to 0?

PME Enable

bypassed on

wake-up event?

No 0 0 0 Yes No

No 1 0 0 Yes Yes

Yes X 1 0 No No