Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual 65

Host Software Interface

6.4.2.3.1 Configuration Parameters

The interpretation of the fields from the configuration byte maps are:

• BYTE 0.

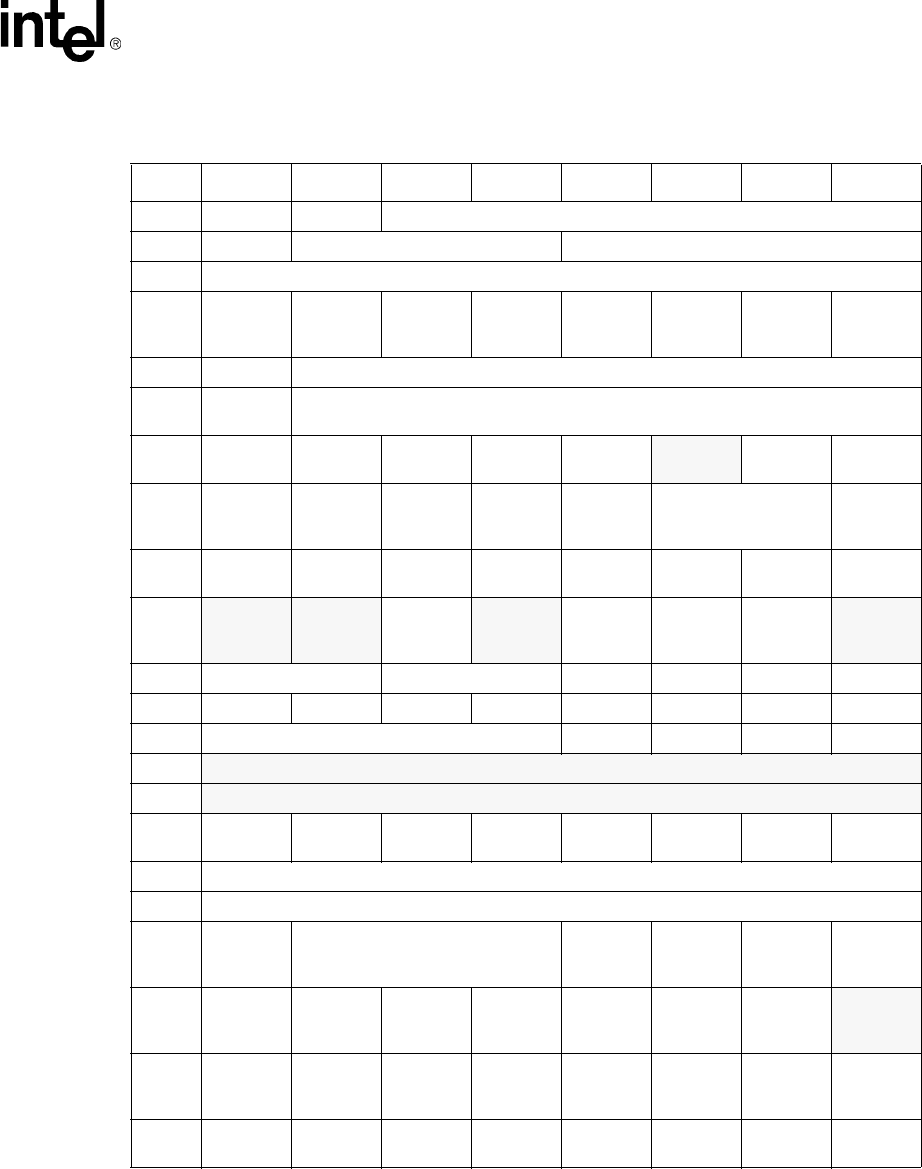

Table 40. 82559 Configuration Byte Map

Byte D7 D6 D5 D4 D3 D2 D1 D0

0 0 0 Byte Count

1 0 Transmit FIFO Limit Receive FIFO Limit

2 Adaptive Interframe Spacing

30000

Term

Write on

CL

Read Al

Enable

Type

Enable

MWI

Enable

4 0 Receive DMA Minimum Byte Count

5

DMBC

Enable

Transmit DMA Maximum Byte Count

6

Save Bad

Frames

Discard

Overruns

Ext. Stat.

Count

Extended

TxCB

CI

Interrupt

TCO

Statistics

10

7

Dynamic

TBD

2 Frames

in FIFO

000Underrun Retry

Discard

Short

Receive

8

CSMA

Disable

0000001

9

0 0

Link

Wake-up

Enable

VLAN

TCO

000

TCP/UDP

Check-

sum

10 Loopback Pre-amble Length NSAI 1 1 0

1100000000

12Interframe Spacing 0001

13

(00000000)

14 (11110010)

15

CRS and

CDT

1

CRC16

(0)

Ignore

U/L

1

Wait After

Win

Broadcast

Disable

Promis-

cuous

16 FC Delay Least Significant Byte

17 FC Delay Most Significant Byte

18 1 Priority FC Threshold

Long

Receive

OK

Receive

CRC

Transfer

Padding Stripping

19

Automatic

FDX

Force

FDX

Reject FC

Receive

FC

Restart

Receive

FC

Restop

Transmit

FC

Magic

Packet

Wake-up

Reserved

20 0

Multiple

IA

Priority

FC

Location

11111

210000

Multicast

All

101