140 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

Wake-up Functionality

A.2 Low Power Modes

The device wake-up capabilities require internal PHY and CSMA blocks to be fully active. When

the controller is set into the D2 or D3 power state and wake up is disabled, the internal PHY and

CSMA units are set into low power modes. In this mode, the device loses the link connection. In

D1, the PHY and CSMA units are always active.

Note: Placing the device into low power mode (D2 or D3 power state) with the PME enable bit cleared

immediately turns off the internal PHY unit. Setting the PME enable bit while the controller is in a

low power state will power up the internal PHY and establish link connection. If the wake up on

link status change feature is enabled, the 82558 (or later generation controller) will wake up the

system. To prevent the above scenario, the PME enable bit should be active before the device is set

into low power mode.

A.3 Power Management Context After Reset

The controller has two hardware reset signals that are both active low:

• RST#. This is the PCI bus reset, which is active on power up of the PCI power source.

• ALTRST#. This is the power on reset (POR) and is active on power up of the auxiliary power

source. It is connected to the system auxiliary power good signal.

The PCI Power Management Specification requires that the PME status and PME enable bits in the

PMCSR will not be cleared by PCI RST# if the function supports wake up from the D3

cold

state. If

the device samples link status (LISTAT) at 0 after a hardware reset, it assumes that an auxiliary

power source is used and wake up from D3

cold

is possible. In this case, assertion of RST# does not

clear these bits.

In order to support Wake on LAN (WOL) mode (preboot wake up), the controller should be able to

generate a wake up event without any software configuration, including PCI power management

configuration. In this scenario, the default configuration of the power management bits should

enable wake up after a hardware reset. The auxiliary power support indication is used to set these

bits after reset.

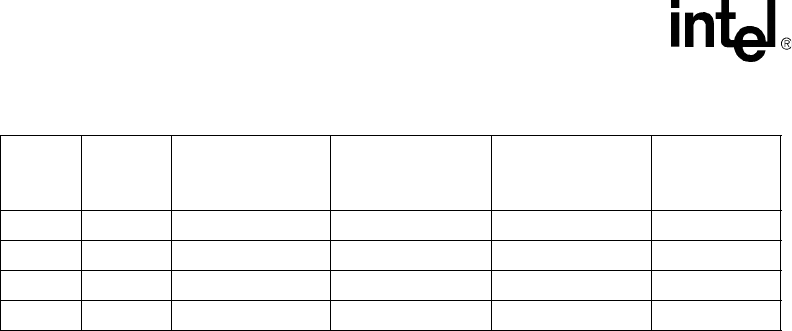

External

Clock

Circuit

Auxiliary

Power

Fixed Filtering

Wake Up

a

a. If the PME enable bit is set in the D0 state, the device will assert PME# for every wake-up event. It is BIOS

responsibility to disable PME# in D0.

Flexible Filtering

Wake Up

Link Status

Change Wake Up

PME Support

in PMC

No No D1, D2, D3h D1 D1, D2, D3h 01111b

No Yes D1, D2, D3h, D3c D1 D1, D2, D3h, D3c 11111b

Yes No D1, D2, D3h D1,D2,D3h D1, D2, D3h 01111b

Yes Yes D1,D2, D3h, D3c D1, D2, D3h, D3c D1,D2, D3h, D3c 11111b