10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual 125

Physical Layer Interface

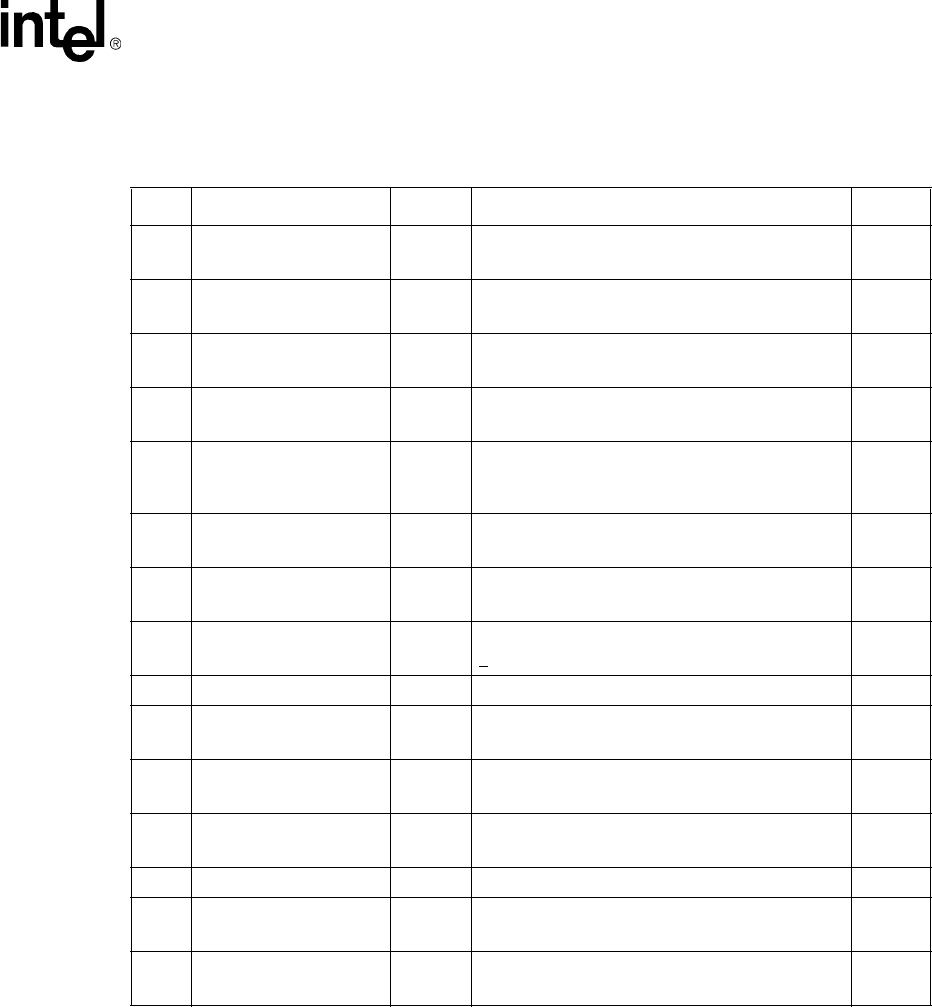

7.3.2 Special Control Register: Register 17

Bit Name R / W Description Default

15 Scrambler Bypass RW

1 = Bypass Scrambler

0 = Normal operation

0

14 4/5 Bypass RW

1 = Bypass 4-bit to 5-bit

0 = Normal operation

0

13 Force Transmit H Pattern RW

1 = Force H pattern

0 = Normal operation

0

12 Force 34 Transmit Pattern RW

1 = Force 34 pattern

0 = Normal operation

0

11 Good Link RW

1 = 100BASE-TX good link indication, forcing to

ASD output

0 = Normal operation

0

9MDI Tristate RW

1 = Tri-state MDI interface

0 = Normal operation

0

8

Dynamic Power Down

Disable

RW

1 = Disable Dynamic Power Down.

0 = Normal operation

0

7

Auto-Negotiation

Loopback

RW

1 = Auto-negotiation loopback

0

= Auto negotiation normal Mode.

0

6 Reserved This bit is reserved. 0

5Filter Bypass RW

1 = Bypass filter

0 = Normal operation

0

4 Auto-Polarity Disable RW

1 = Disable auto-polarity

0 = Normal operation

0

3 Squelch Test Disable RW

1 = Disable 10BASE-T squelch test

0 = Normal squelch operation

0

2 Extended Squelch RW This bit indicates extended squelch control 0

1 Link Integrity Disable RW

1 = Disable link integrity operation

0 = Normal link integrity operation

0

0 Jabber Function disable RW

1 = Disable jabber function

0 = Normal jabber operation.

0