Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual 13

PCI Interface

4.1.5 Revision (Offset 8)

This register specifies a device specific revision identifier. For the 82557 C-Step, 82558, and

82559, this field may be automatically loaded from the EEPROM at power on or upon the assertion

of a PCI reset. The default revision register values for the various devices are:

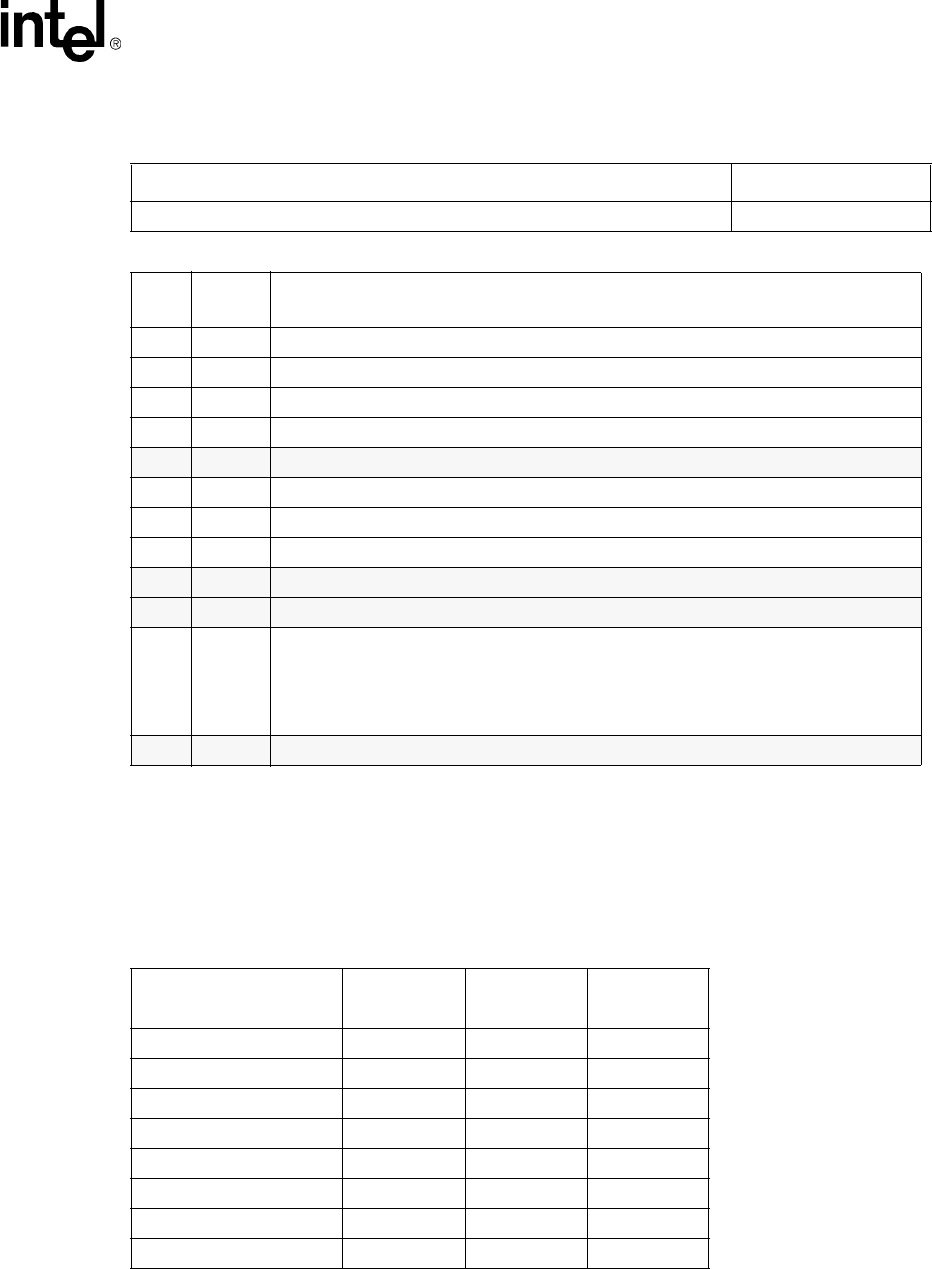

Figure 3. Command Register

15 43 0

Status Bits Reserved

Bits

Initial

Value

Description

15 x Detected parity error.

14 x Signaled system error.

13 x Received master abort.

12 x Received target abort.

11 0 Signaled target abort.

10:9 01 DEVSEL timing (indicates minimum timing).

8 x Data parity reported.

7 1 Fast back-to-back capable.

6 0 UDF supported.

5 0 66 MHz capable.

4

1 (82559

and

82558)

0

(82557)

Capabilities list. This bit indicates whether the device implements a list of new capabilities

such as PCI Power Management. If it is set, the Cap_Ptr register in the PCI Configuration

Space points to the location of the first item in the Capabilities List.

NOTE: This bit is set to 1 for the 82559 and 82558 if it is not disabled by the EEPROM. It

is always equal to 0 for the 82557.

3:0 0 Reserved.

Table 2. Device and Revision ID

Device Revision ID

PCI Revision

Supported

Intel Driver

Supported

82557 A-Step 01h 2.0 Yes

82557 B-Step 02h 2.0 Yes

82557 C-Step 03h 2.1 No

82558 A-Step 04h 2.1 Yes

82558 B-Step 05h 2.1 Yes

82559 A-Step 06h 2.1 No

82559 B-Step 07h 2.1 No

82559 C-Step 08h 2.2 Yes