42 Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

Host Software Interface

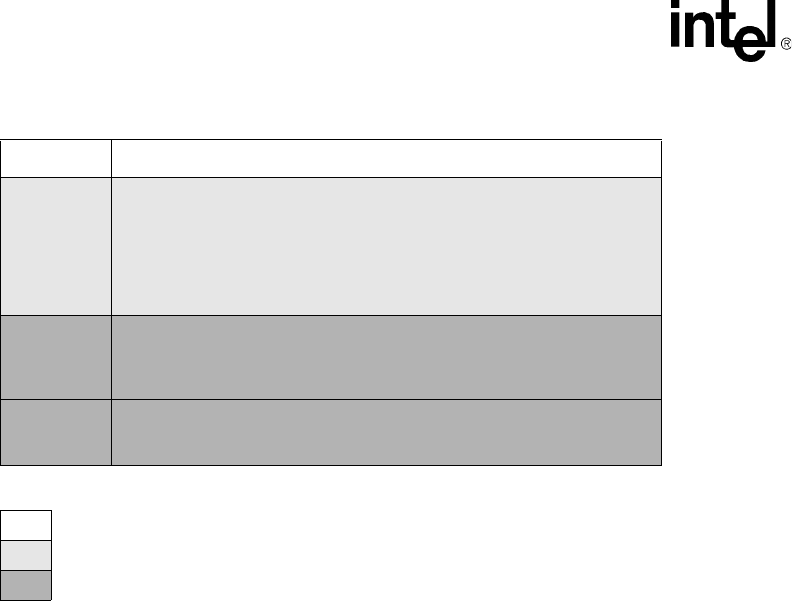

As the above table indicates, the 8255x track of 16 different statistics. However, the 82558 also

maintains three additional statistics (lightly shaded in the above table) for a total of 19 counters. In

addition to the 19 statistics maintained by the 82558, the 82559 tracks two additional statistics and

six reserved statistics (indicated by darker shading in the above table).

The counters are initially set to zero by the device after reset. They cannot be preset to anything

other than zero. The device increments the counters by internally reading them, incrementing them,

and writing them back. This process is invisible to the CPU and PCI bus. In addition, the counters

adhere to the following rules:

• The counters are wrap around counters. After reaching 0FFFFFFFFh, the counters wrap

around to 0. There is no indication when the counters wrap around to 0. Software must track

this.

• The device updates the required counters for each frame. It is possible for more than one

counter to be updated as multiple errors can occur in a single frame.

• The counters are 32 bits wide and their behavior is fully compatible with the IEEE 802.1

standard. The device supports all mandatory and recommended statistics functions through the

status of the receive header and directly through these statistics counters.

Software can access the counters by issuing a Dump Statistical Counters SCB command. This

provides a snapshot, in main memory, of the internal statistical counters. For the 82557, this dump

always consists of 16 statistics. For the 82558 and 82559, this dump may contain more statistics

depending on how the device is configured. It is recommended for software to use the following

sequence for maintaining its own statistics:

1. Allocate an array in host memory large enough to hold all of the statistics dumped plus one

additional Dword for status information (for example, 68 bytes for the 82557). This memory

space must be Dword aligned.

2. Load the absolute address of this location into the device using the Load Dump Counters

Address command.

72

Flow control receive unsupported. This counter contains the number of

MAC frames received by the device that are not flow control pause frames.

These frames are valid MAC frames with the predefined MAC type value

and a valid address; however, they contain an unsupported opcode. In

multimedia mode this counter tracks the pause low frames received. This

count includes both the XOFF_Low frames received and XON_Low frames

(PAUSE_Low(0)) received.

76

Transmit TCO frames. This counter is incremented when the 82559

transmits a packet initiated by the TCO controller (or ICH device). It should

be noted that any transmission of TCO packets also affects the normal

transmit counters.

78

Receive TCO frames. This counter is incremented when the 82559

receives a TCO packet. It should be noted that any reception of TCO

packets also affects the normal receive counters.

Applicable to all controllers.

Applicable only to 82558 and later generation controllers.

Applicable only to 82559 and later generation controllers.

Table 17. Statistical Counters

Byte Offset Device Statistic