Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual 29

Host Software Interface

6.2 Initializing the LAN Controller

A hardware or software reset prepares the 8255x for normal operation. Since the PCI Specification

already provides automatic configuration of many critical parameters such as I/O, memory

mapping and interrupt assignment, the device is set to an operational default state after reset.

However, the device cannot transmit or receive frames until a Configure command is issued.

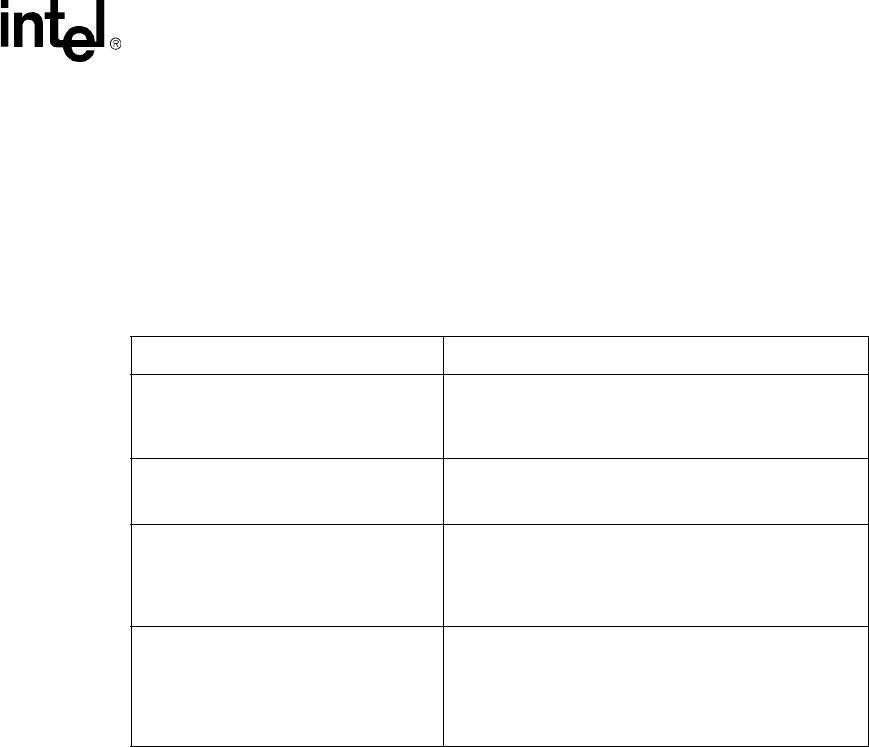

Different reset commands affect the controller in different ways as detailed by the table below.

The phrase “Software Reset” will be used throughout this manual to indicate a complete reset using

the Port Reset command, unless specified otherwise. Port commands are discussed in detail in

Section 6.3.3, “PORT Interface”.

6.2.1 LAN Controller Addressing Format

The 8255x supports a 32-bit enhanced linear addressing mode and 32-bit segmented addressing

mode. The 8255x accommodates both types of addressing schemes with the enhanced linear

addressing mode. The controller always calculates a physical address by adding the appropriate 32-

bit BAR (CU base or RU base) to a 32-bit offset. This allows a linear addressing scheme to be used

by setting the base address to zero and using the full 32-bit offset registers to indicate the linear

address. A 32-bit segmented scheme can be used as well by programming the appropriate 32-bit

base address register and using the lower 16 bits of the 32-bit offset. This is illustrated in the table

below.

Table 8. Reset Commands

Reset Operation Effect on LAN Controller

Hardware reset. This occurs when the

Reset pin (RST#) is asserted. (This is

caused by turning the system on or by

pressing the system reset button.)

Resets all internal registers. A full initialization sequence

is needed to make the device operational.

Software reset. (This is issued as Port

Reset command.)

Resets all internal registers, except the PCI configuration

registers. A full initialization sequence is needed to make

the device operational.

Selective reset. (This is issued as Port

Selective Reset command.)

Maintains PCI configuration, RU and CU base registers,

HDS size, error counters, configure, IA setup and

multicast setup command information. RU and CU are set

to the idle state. All other setup and configuration

information is lost.

Self test. (This is issued as a Port Self

Test command.)

Resets all internal registers except for the PCI

configuration registers. A full initialization sequence is

needed to make the device operational. A selective reset

is issued internally before the command is executed. A

software reset is issued internally after the command is

completed.