Video Capture Registers

Video Capture Port3-78 SPRU629

3.13.16 TSI System Time Clock Compare LSB Register (TSISTCMPL)

The transport stream interface system time clock compare LSB register

(TSISTCMPL) is used to generate an interrupt at some absolute time based

on the STC. TSISTCMPL holds the 32 least-significant bits (LSBs) of the

absolute time compare (ATC). Whenever the value in TSISTCMPL and

TSISTCMPM match the unmasked bits of the time kept by the STC hardware

counter and the STEN bit in TSICTL is set, the STC bit in VPIS is set.

TSISTCMPL is shown in Figure 3–44 and described in Table 3–29.

To prevent inaccurate comparisons caused by changing register bits, the

software should disable the system time clock interrupt (clear the STEN bit in

TSICTL) prior to writing to TSISTCMPL.

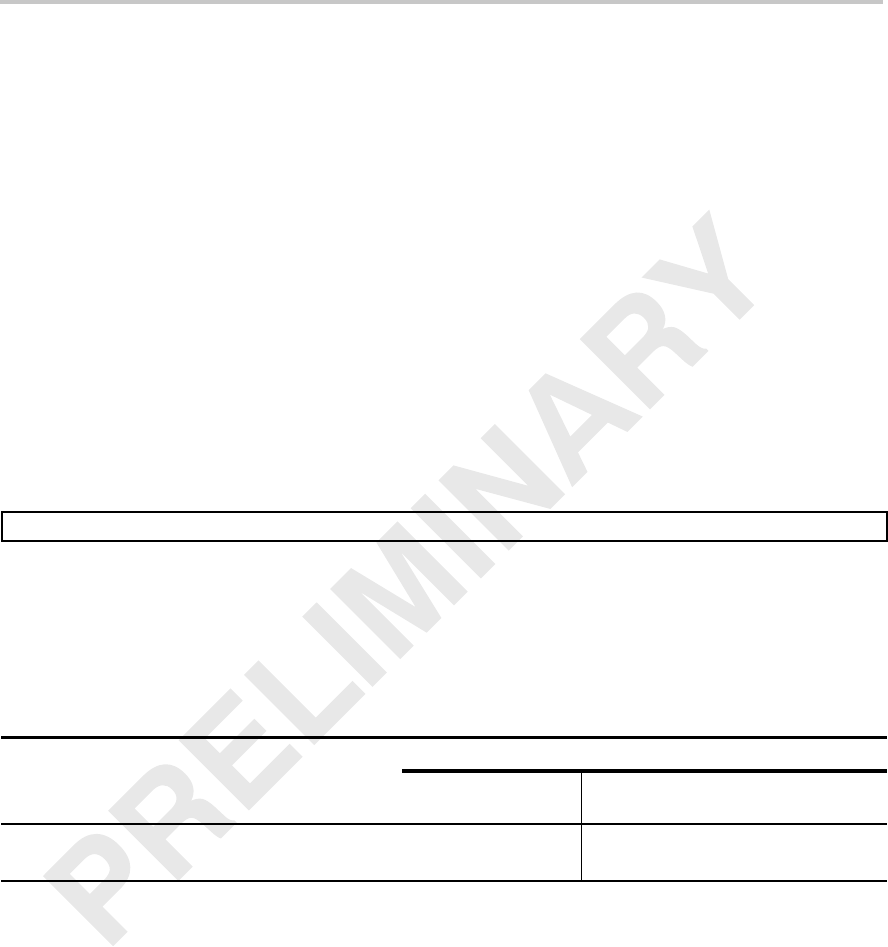

Figure 3–44. TSI System Time Clock Compare LSB Register (TSISTCMPL)

31 0

ATC

R/W-0

Legend: R/W = Read/Write; -n = value after reset

Table 3–29. TSI System Time Clock Compare LSB Register (TSISTCMPL)

Field Descriptions

Description

Bit Field symval

†

Value

BT.656, Y/C Mode,

or Raw Data Mode

TSI Mode

31–0 ATC OF(value) 0–FFFF FFFFh Not used. Contains the 32 LSBs of the

absolute time compare.

†

For CSL implementation, use the notation VP_TSISTCMPL_ATC_symval