GPIO Registers

5-23General Purpose I/O OperationSPRU629

5.1.11 Video Port Pin Interrupt Status Register (PISTAT)

The video port pin interrupt status register (PISTAT) is shown in Figure 5–11

and described in Table 5–12. PISTAT is a read-only register that indicates the

GPIO pin that has a pending interrupt.

A bit in PISTAT is set when the corresponding GPIO pin is configured as an

interrupt (the corresponding bit in PIEN is set, the pin is enabled for GPIO in

PFUNC, and the pin is configured as an input in PDIR) and the appropriate

transition (as selected by the corresponding PIPOL bit) occurs on the pin.

Whenever a PISTAT bit is set to 1, the GPIO bit in VPIS is set. The PISTAT bits

are cleared by writing a 1 to the corresponding bit in PICLR. Writing a 0 has

no effect. Clearing all the PISTAT bits does not clear the GPIO bit in VPIS, it

must be explicitly cleared. If any bits in PISTAT are still set when the GPIO bit

is cleared, the GPIO bit is set again.

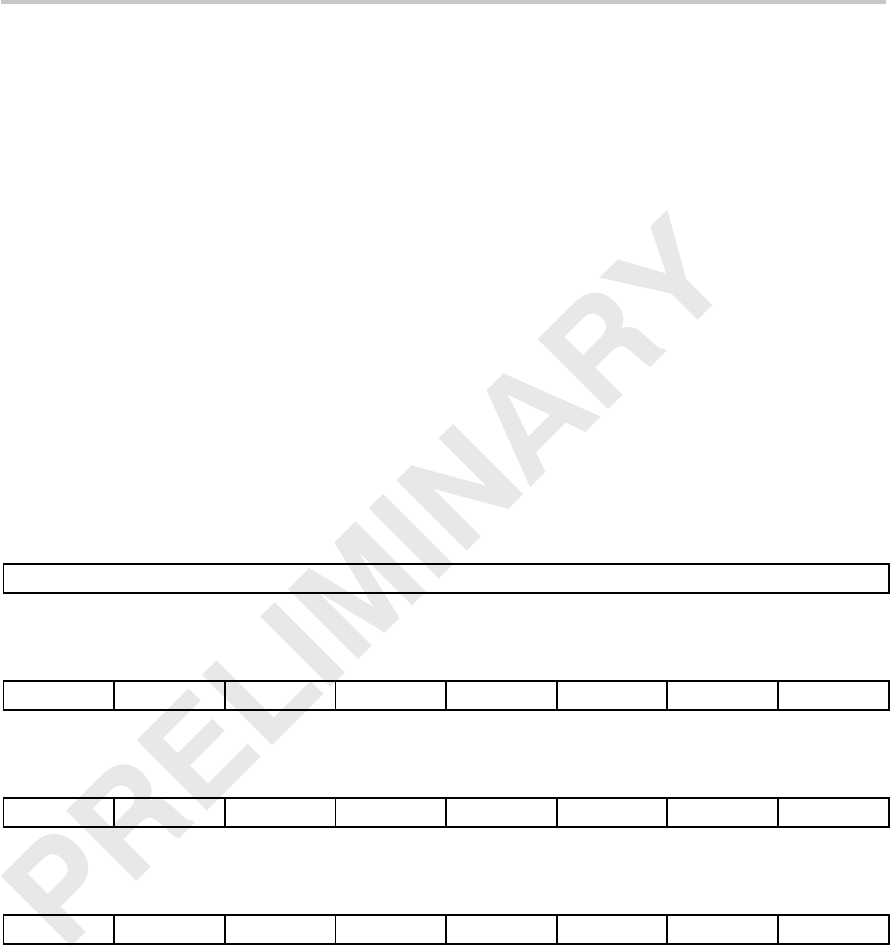

Figure 5–11.Video Port Pin Interrupt Status Register (PISTAT)

31 24

Reserved

R-0

23 22 21 20 19 18 17 16

Reserved

PISTAT22 PISTAT21 PISTAT20 PISTAT19 PISTAT18 PISTAT17 PISTAT16

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

15 14 13 12 11 10 9 8

PISTAT15

PISTAT14 PISTAT13 PISTAT12 PISTAT11 PISTAT10 PISTAT9 PISTAT8

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

76543210

PISTAT7

PISTAT6 PISTAT5 PISTAT4 PISTAT3 PISTAT2 PISTAT1 PISTAT0

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

Legend: R = Read only; -n = value after reset