www.ti.com

EMAC Port Registers

5.27 Receive Channel 0-7 Flow Control Threshold Register (RXnFLOWTHRESH)

The receive channel 0-7 flow control threshold register (RXnFLOWTHRESH) is shown in Figure 69 and

described in Table 63.

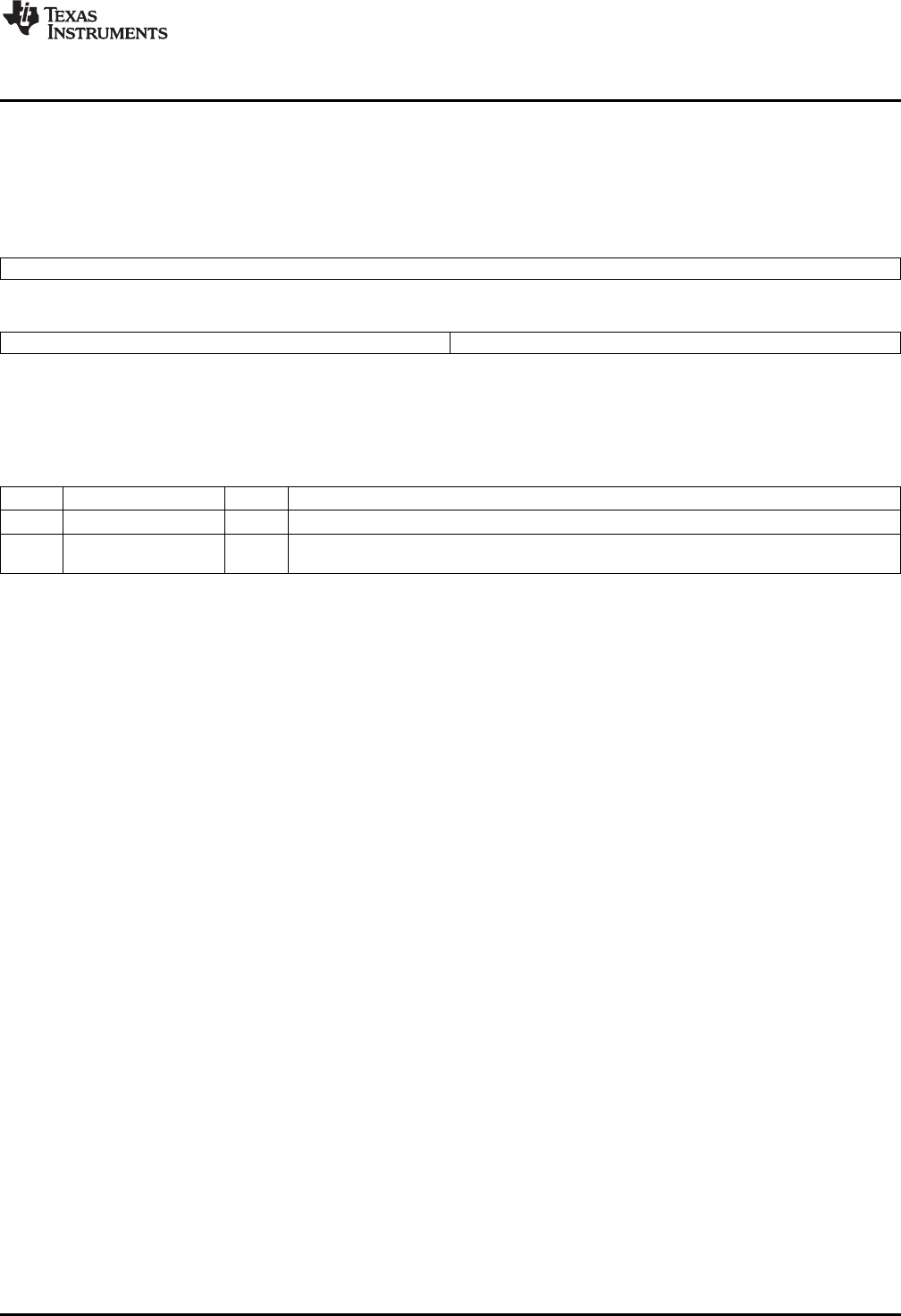

Figure 69. Receive Channel n Flow Control Threshold Register (RXnFLOWTHRESH)

31 16

Reserved

R-0

15 8 7 0

Reserved RXnFLOWTHRESH

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 63. Receive Channel n Flow Control Threshold Register (RXnFLOWTHRESH) Field

Descriptions

Bit Field Value Description

31-8 Reserved 0 Reserved

7-0 RXnFLOWTHRESH Receive flow threshold. These bits contain the threshold value for issuing flow control on

incoming frames for channel n (when enabled).

123

SPRUEF8F–March 2006–Revised November 2010 C6472/TCI6486 EMAC/MDIO

Submit Documentation Feedback

Copyright © 2006–2010, Texas Instruments Incorporated