EMAC Port Registers

www.ti.com

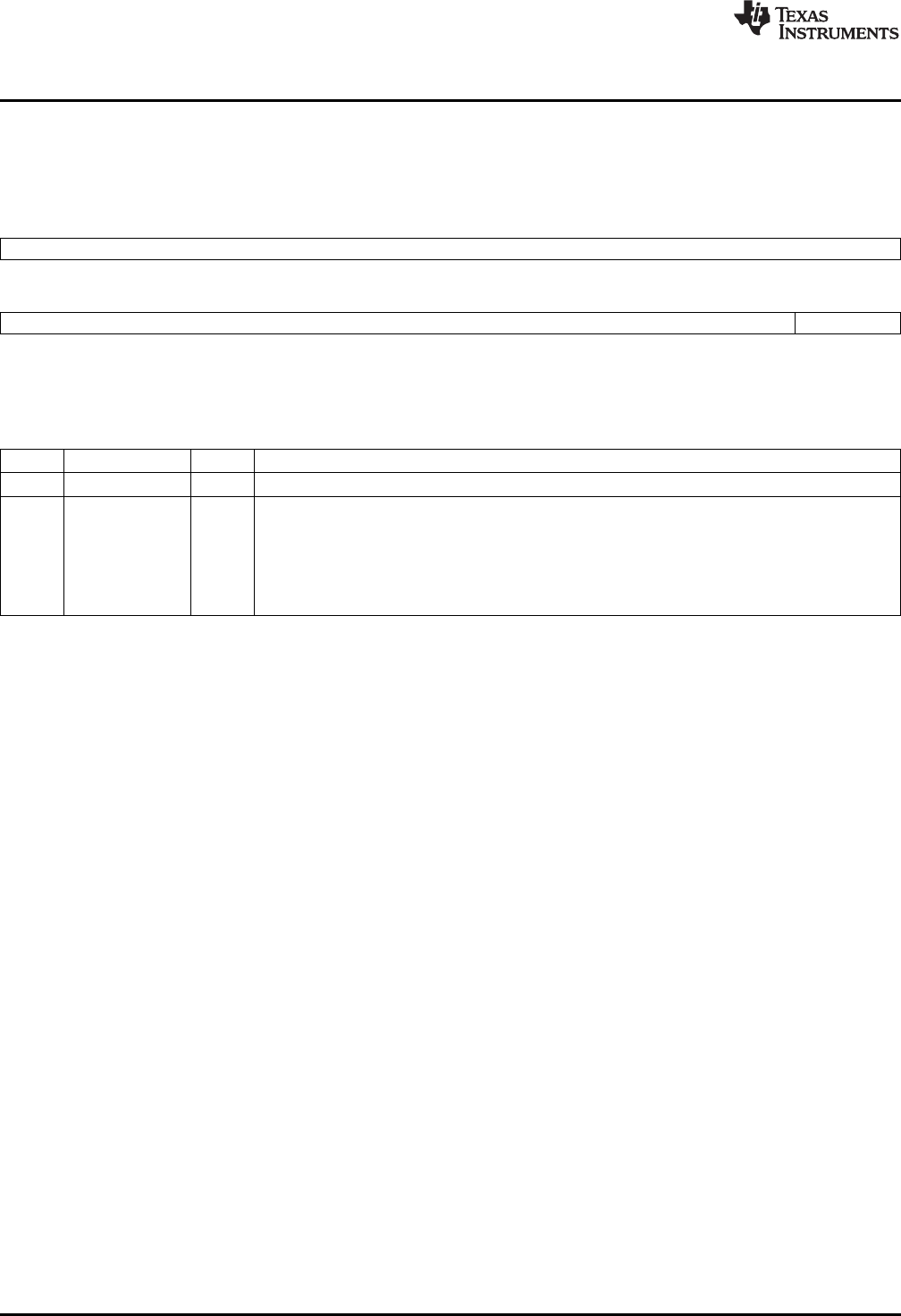

5.34 Soft Reset Register (SOFTRESET)

The soft reset register (SOFTRESET) is shown in Figure 76 and described in Table 70.

Figure 76. Soft Reset Register (SOFTRESET)

31 16

Reserved

R-0

15 1 0

Reserved SOFTRESET

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 70. Soft Reset Register (SOFTRESET) Field Descriptions

Bit Field Value Description

31-1 Reserved 0 Reserved

0 SOFTRESET Software reset. Writing a one to this bit causes the EMAC logic to be reset. Software reset occurs

when the receive and transmit DMA controllers are in an idle state to avoid locking up the

Configuration bus. After writing a one to this bit, it may be polled to determine if the reset has

occurred. If a one is read, the reset has not yet occurred. If a zero is read, then reset has occurred.

0 A software reset has not occurred

1 A software reset has occurred

132

C6472/TCI6486 EMAC/MDIO SPRUEF8F–March 2006–Revised November 2010

Submit Documentation Feedback

Copyright © 2006–2010, Texas Instruments Incorporated