EMAC Port Registers

www.ti.com

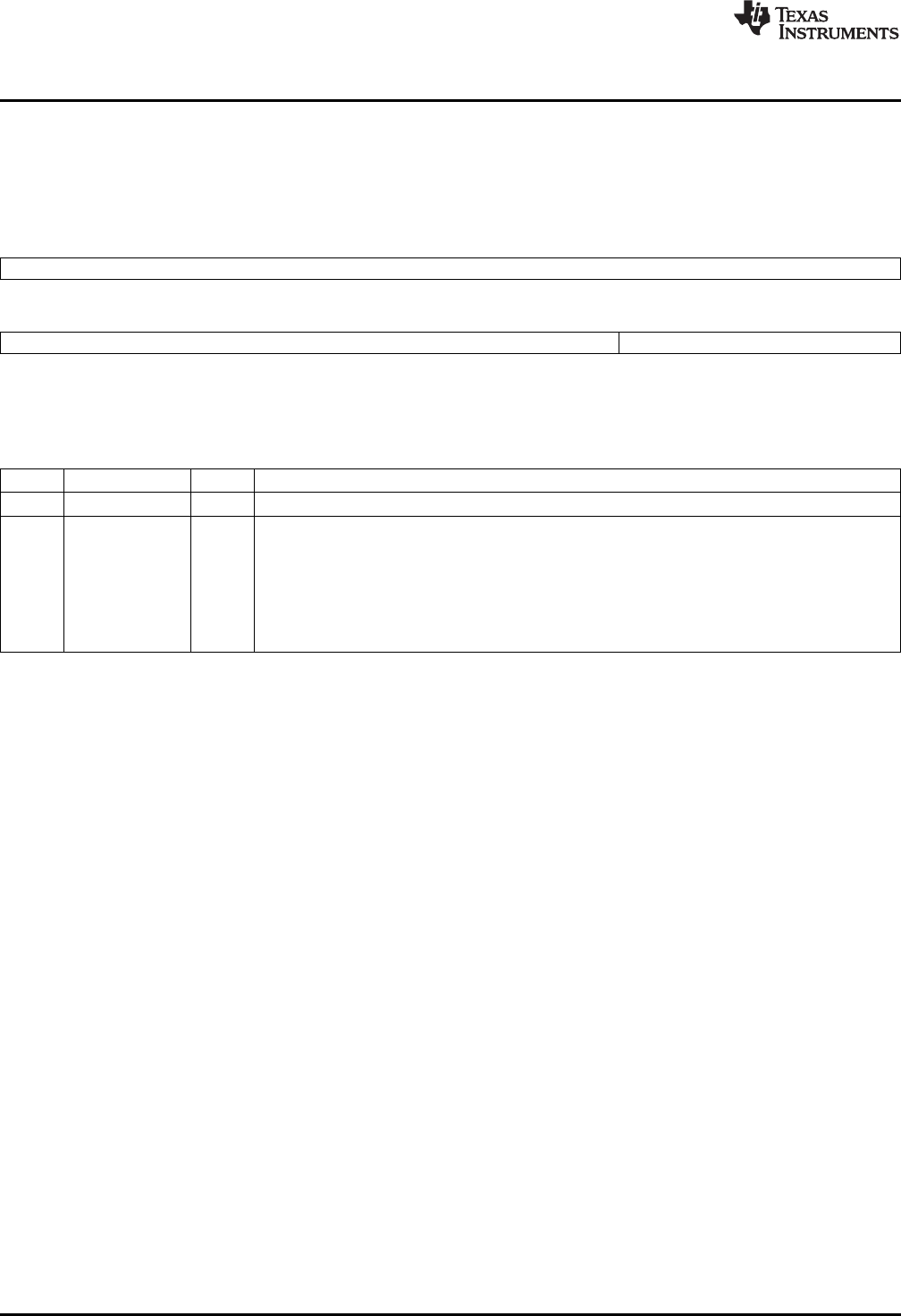

5.40 Transmit Pacing Algorithm Test Register (TPACETEST)

The transmit pacing algorithm test register (TPACETEST) is shown in Figure 82 and described in

Table 76.

Figure 82. Transmit Pacing Algorithm Test Register (TPACETEST)

31 16

Reserved

R-0

15 5 4 0

Reserved PACEVAL

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 76. Transmit Pacing Algorithm Test Register (TPACETEST) Field Descriptions

Bit Field Value Description

31-5 Reserved 0 Reserved

4-0 PACEVAL Pacing register current value. A nonzero value in this field indicates that transmit pacing is active. A

transmit frame collision or deferral causes PACEVAL to be loaded with 1Fh (31); good frame

transmissions (with no collisions or deferrals) cause PACEVAL to be decremented down to 0.

When PACEVAL is nonzero, the transmitter delays four Inter Packet Gaps between new frame

transmissions after each successfully transmitted frame that had no deferrals or collisions. If a

transmit frame is deferred or suffers a collision, the IPG time is not stretched to four times the

normal value. Transmit pacing helps reduce capture effects, which improves overall network

bandwidth.

138

C6472/TCI6486 EMAC/MDIO SPRUEF8F–March 2006–Revised November 2010

Submit Documentation Feedback

Copyright © 2006–2010, Texas Instruments Incorporated