www.ti.com

EMIC Module Registers

3.3.2 TPSTAT Registers

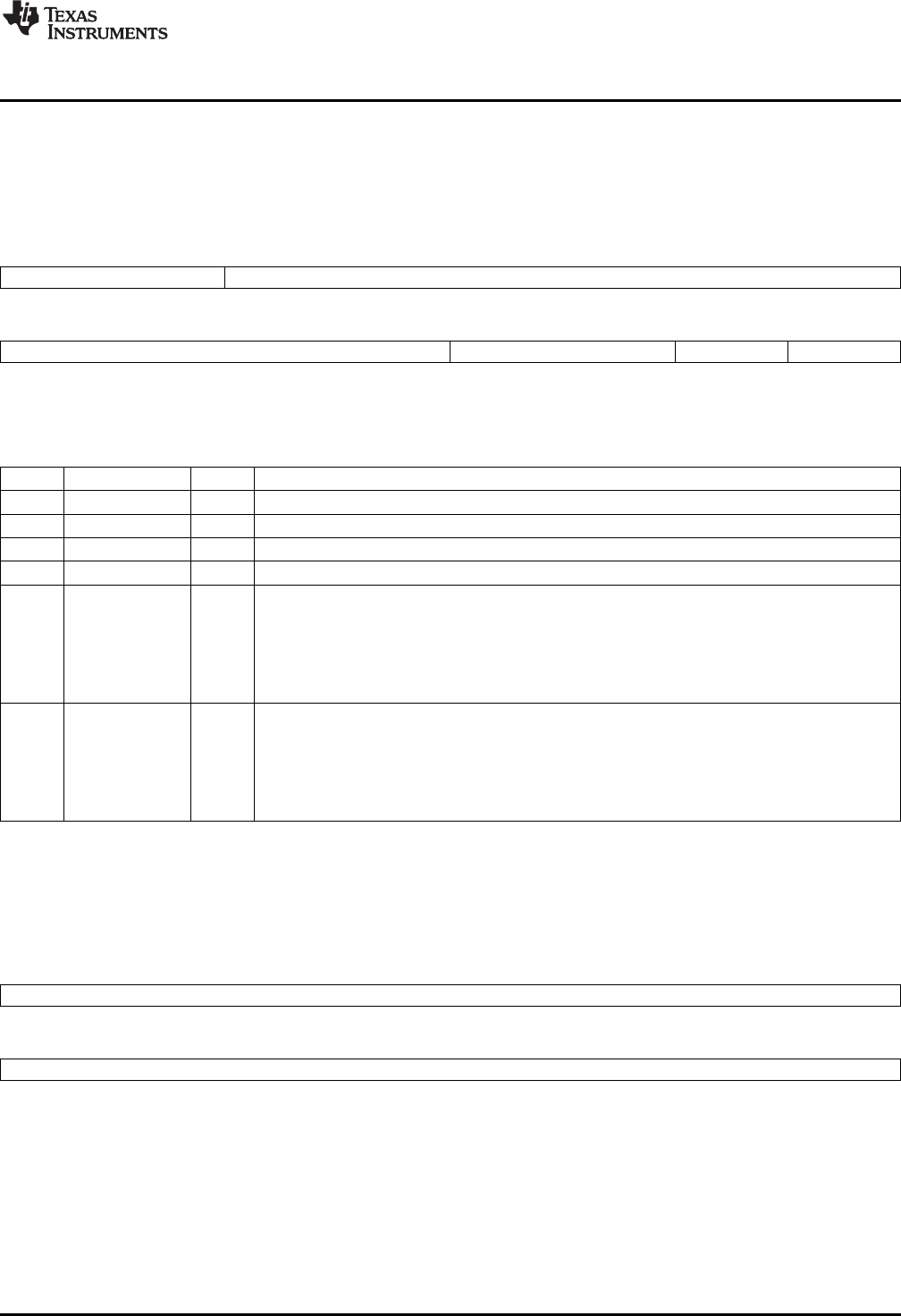

There are eight TPSTAT registers (TPSTAT0 through TPSTAT7), one per transmit event. This register

configuration is common to all C64x+mega modules. The TPSTAT register details are shown in Figure 27

and described in Table 20.

Figure 27. TPSTAT Register

31 28 27 16

Reserved TIME

0000 R-0000 0000

15 8 7 4 3 2 1 0

CNT Reserved TIM_SM DIV_SM

R-0000 0000 0000 R-00 R-00

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 20. TPSTAT Register Field Descriptions

Bit Field Value Description

31-28 Reserved Reserved

27-16 TIME Current time delay value

15-8 CNT Current divide by N value

7-4 Reserved Reserved

3-2 TIM_SM Time delay SM

00 Time delay SM in WAITING state

01 Time delay SM in DELAY state

10 Time delay SM in OUTPUT state

11 Reserved

1-0 DIV_SM Divide by N SM

00 Divide by N SM in WAITING state

01 Divide by N SM in DELAY state

10 Divide by N SM in OUTPUT state

11 Reserved

3.4 Prescalar Configuration Register (PSCFG)

There is a single PSCFG register for the wrapper. It contains the reload value for the prescalar

configuration value. The PSCFG register is shown in Figure 28.

Figure 28. Prescalar Configuration Register (PSCFG)

31 16

Reserved

0000 0000

15 0

PRESCALE_CFG

R/W-0000 0000

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

75

SPRUEF8F–March 2006–Revised November 2010 C6472/TCI6486 EMAC/MDIO

Submit Documentation Feedback

Copyright © 2006–2010, Texas Instruments Incorporated